## Materialsammlung Grundlagen der Rechnerarchitektur — Neuere Entwicklungen in der Informationstechnologie

Prof. Dr. Hans-Jürgen Buhl

2003

Fachbereich Mathematik (7) Institut für Angewandte Informatik Bergische Universität – Gesamthochschule Wuppertal

> Interner Bericht der Integrierten Arbeitsgruppe Mathematische Probleme aus dem Ingenieurbereich IAGMPI – 9305

> > Juli 2003 6. Auflage, 2003

Praktische Informatik 01

## Inhaltsverzeichnis

| 1 | Rec  | hnerarchitekturen 1                                                             |

|---|------|---------------------------------------------------------------------------------|

|   | 1.1  | Der von-Neumann-Rechner                                                         |

|   | 1.2  | Modularer Aufbau von Betriebssystemen                                           |

|   | 1.3  | CISC/RISC                                                                       |

|   |      | 1.3.1 CISC                                                                      |

|   |      | 1.3.2 "Überalterung" von CISC                                                   |

|   |      | 1.3.3 RISC (= reduced instruction set computer)-Designprinzip 48                |

|   |      | 1.3.4 Historischer CISC-RISC CPU-Vergleich 52                                   |

|   | 1.4  | Der Cache zur Datentransferbeschleunigung 64                                    |

|   | 1.5  | Multitasking                                                                    |

|   | 1.6  | Bussysteme — Chipsätze und das Motherboard 68                                   |

|   | 1.7  | Der Weg fort von der von-Neumann-Architektur 69                                 |

|   |      | 1.7.1 SPARC                                                                     |

|   |      | 1.7.2 Der Intel Pentium                                                         |

|   | 1.8  | IA64 - Die EPIC-Architektur                                                     |

|   | 1.0  | 1.8.1 Itanium                                                                   |

|   | 1.9  | AMDs 64-Bit-Architektur                                                         |

|   |      | PentiumM                                                                        |

|   | 1.11 | Zukünftige Entwicklungen                                                        |

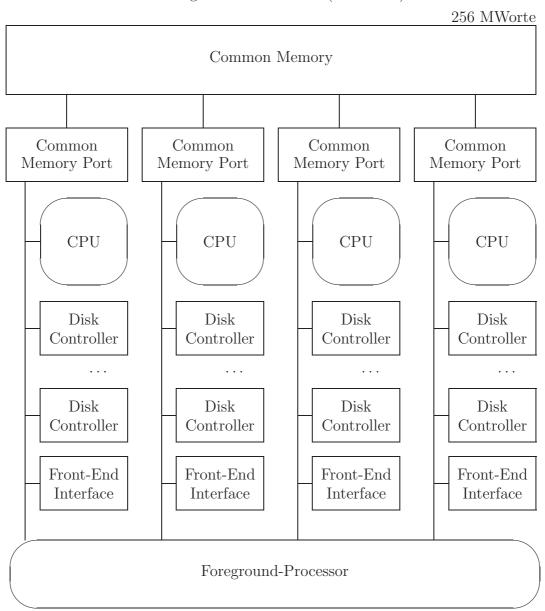

| 2 | Unt  | ernehmensserver und High Performance Computer 99                                |

|   | 2.1  | Serverarchitektur in Unternehmensnetzwerken 99                                  |

|   | 2.2  | Vektorrechner                                                                   |

|   | 2.3  | SIMD- und MIMD-Parallelrechner                                                  |

|   | 2.4  | Mehrprozessorsysteme                                                            |

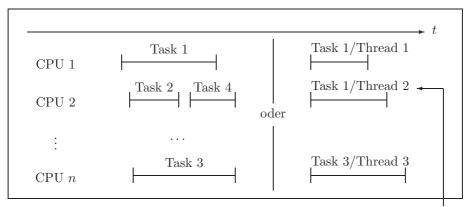

|   | 2.5  | Multithreadsysteme                                                              |

|   | 2.6  | Multiprozessor-Server                                                           |

|   | 2.7  | Clustercomputing und Lastverteilung                                             |

|   | 2.8  | Großrechner und High End Server: Partitionierung der Resourcen, Grid Container, |

| 3 | Rec | chnerar | rchitekturen – Fortsetzung: Peripherie | 116 |

|---|-----|---------|----------------------------------------|-----|

|   | 3.1 | Periph  | neriebus: USB, Firewire und PCI        | 116 |

|   |     | 3.1.1   | USB = Universal Serial Bus             | 116 |

|   |     | 3.1.2   | Firewire, IEEE 1394                    | 117 |

|   |     | 3.1.3   | USB2                                   | 117 |

|   |     | 3.1.4   | Firewire b, IEEE 1394b                 | 117 |

|   |     | 3.1.5   | PCI-X und PCIe                         | 117 |

## Abbildungsverzeichnis

| 1.1  | Computersystem                         |

|------|----------------------------------------|

| 1.2  | Der ZUSE Z3 von Konrad Zuse 6          |

| 1.3  | Universalrechner im Aufbau             |

| 1.4  | "circuit switched" Datentransfer       |

| 1.5  | Datentypen                             |

| 1.6  | Verteilung UNICODE                     |

| 1.7  | Bidirectional Ordering                 |

| 1.8  | General Scripts                        |

| 1.9  | Die Bytes im Speicher                  |

| 1.10 | und ihre Reihenfolge im Computerwort   |

| 1.11 | CPU                                    |

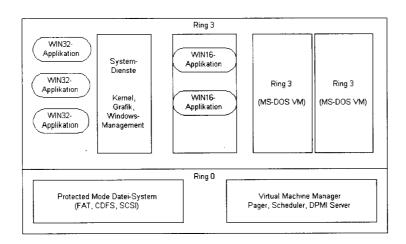

| 1.12 | Windows 95/98                          |

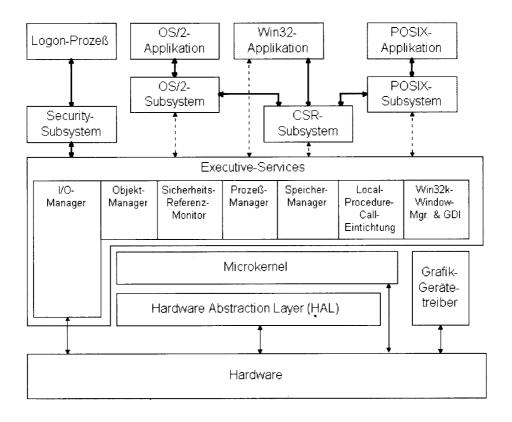

|      | Windows NT                             |

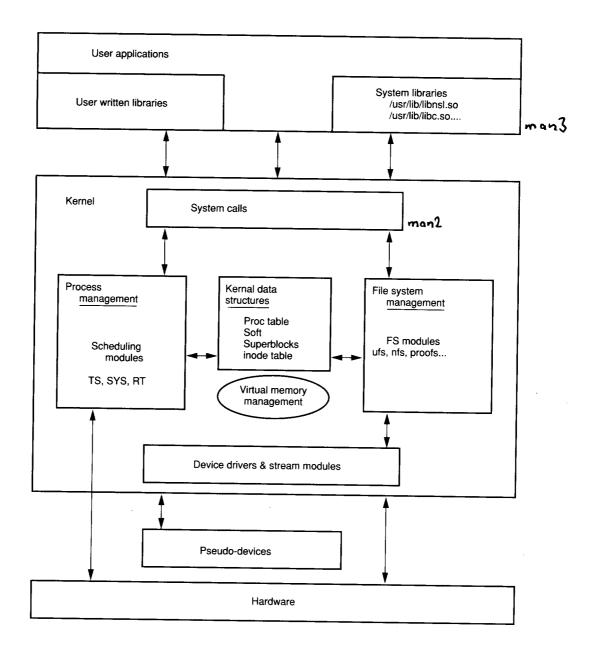

| 1.14 | Solaris/Linux                          |

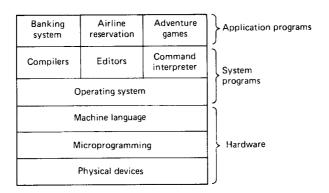

|      | Microcode und Betriebssystem           |

| 1.16 | CISC-CPU-Aufbau                        |

| 1.17 | Microprogrammierte CISC-CPU            |

|      | Nanoprogrammierte CISC-CPU             |

| 1.19 | Der x86 MOV-Befehl                     |

|      | Der x86 MUL-Befehl                     |

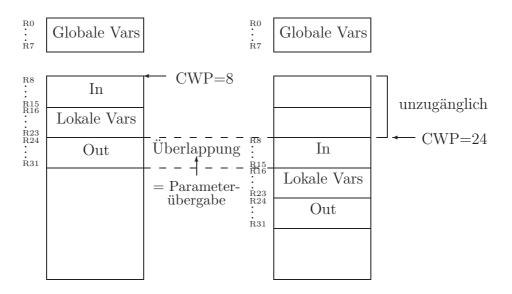

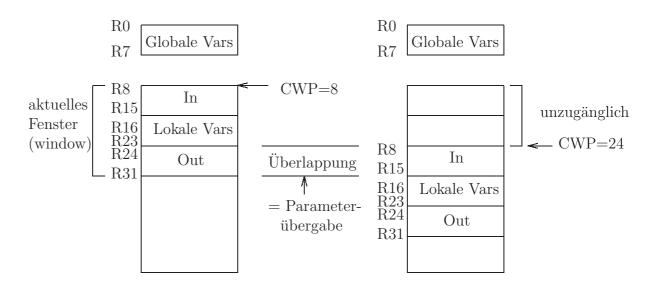

| 1.21 | Registerstack am Beispiel SPARC 51     |

| 1.22 | Der Cache als Daten-Vorratsbehälter    |

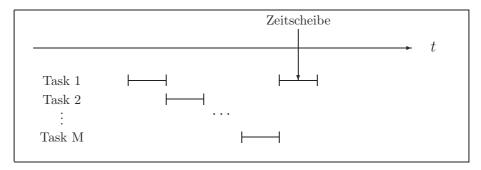

| 1.23 | Multitask-Stati                        |

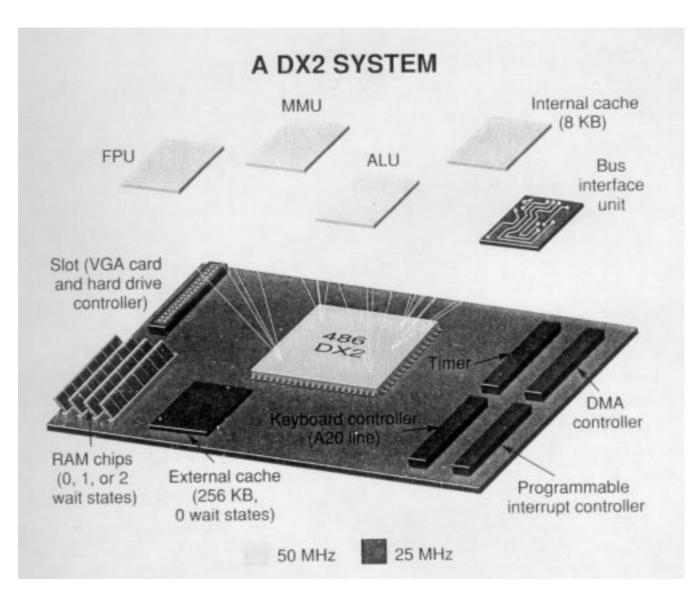

| 1.24 | Cache auf dem Motherboard              |

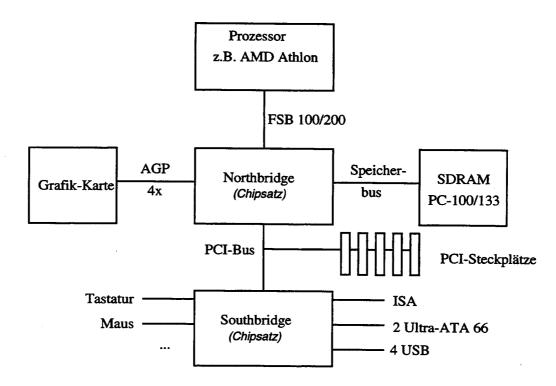

| 1.25 | PC Frontsidebus                        |

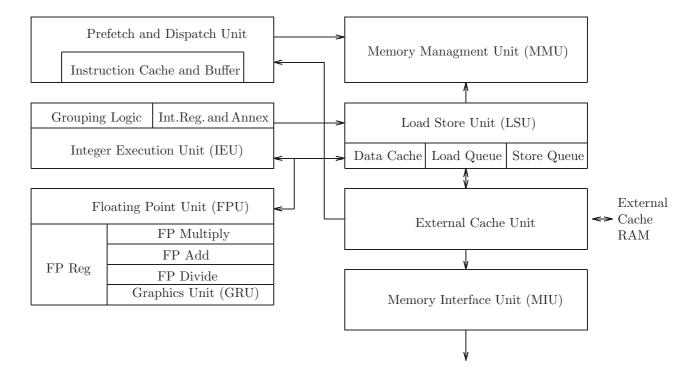

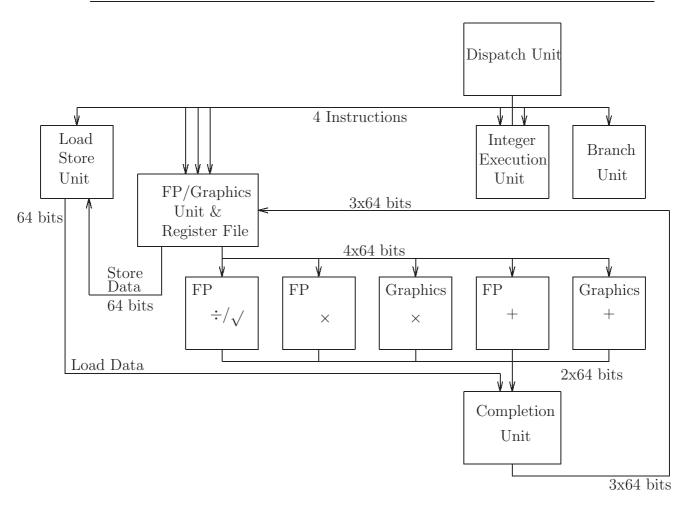

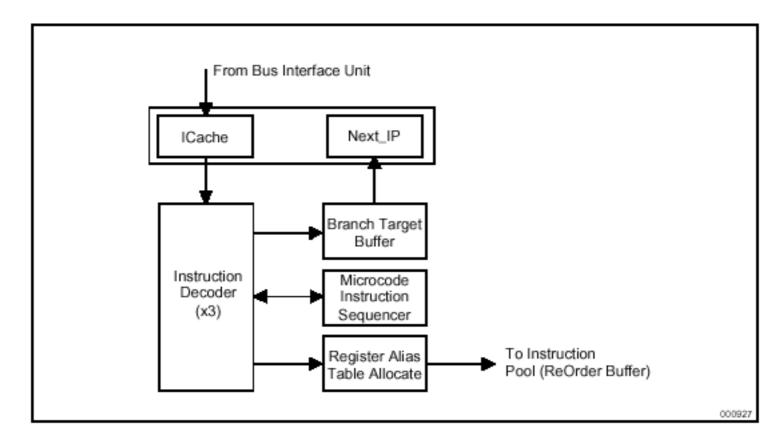

| 1.26 | PentiumII Execution Units              |

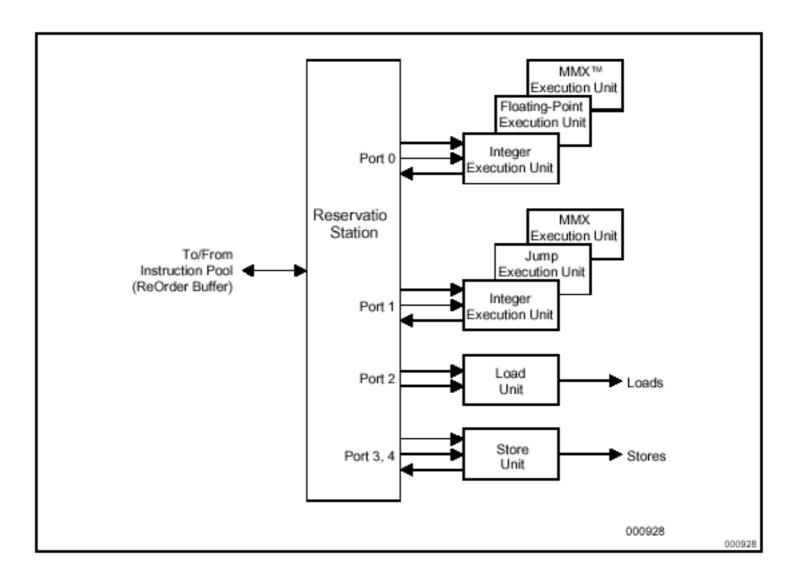

|      | PentiumII-Design 1                     |

| 1.28 | PentiumII-Design 2                     |

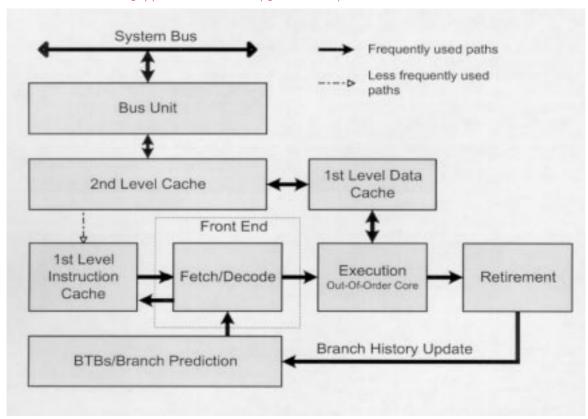

|      | P6 Architektur                         |

|      | Dynamic Execution Microarchitecture 89 |

| 1.31 | x86-Entwicklung                        |

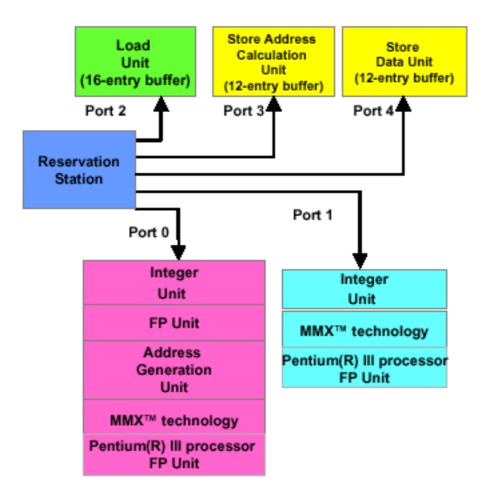

| 1.32 | PentiumIII und 4                                     |

|------|------------------------------------------------------|

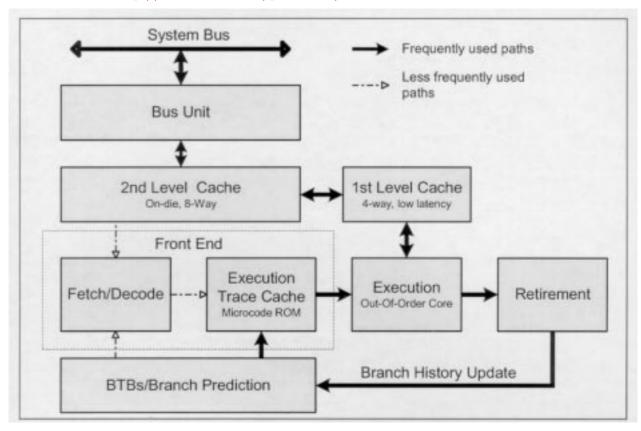

| 1.33 | NetBurst Architektur                                 |

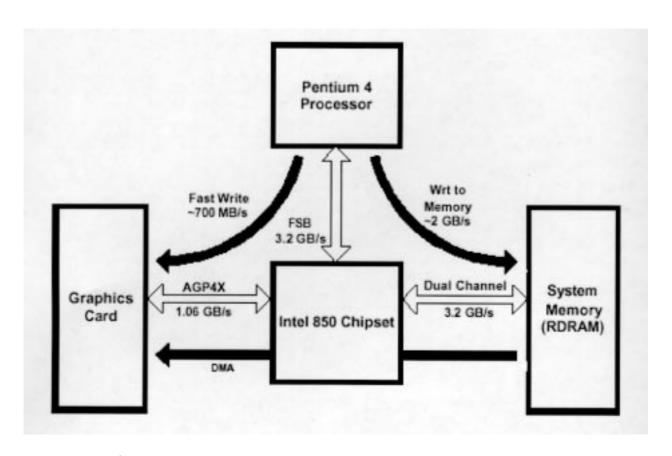

| 1.34 | Datendurchsatz beim Pentium4                         |

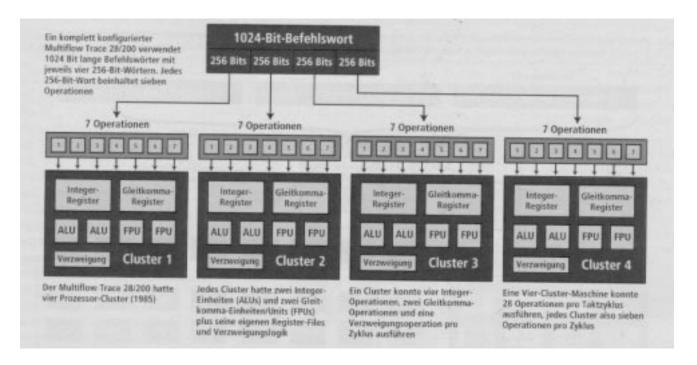

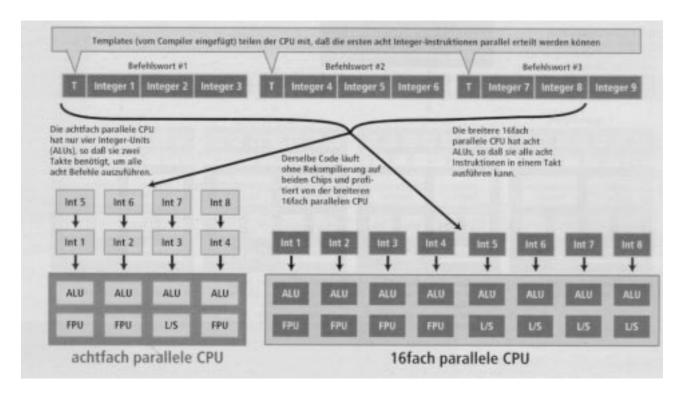

| 1.35 | VLIW                                                 |

| 1.36 | IA64                                                 |

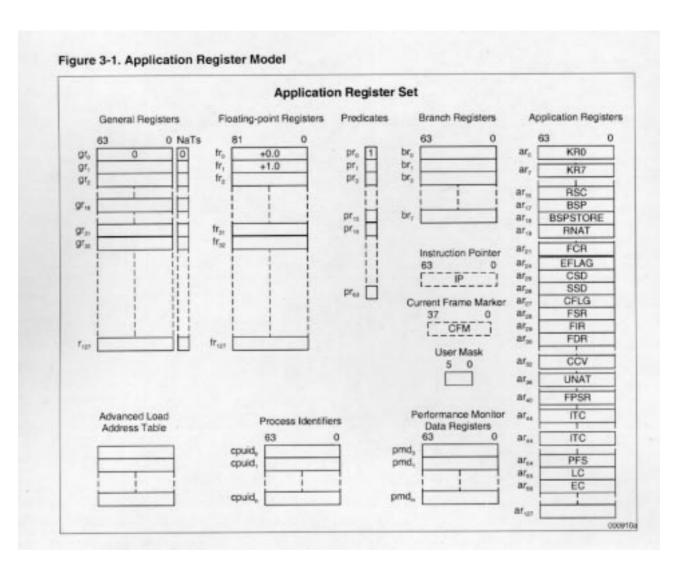

| 1.37 | Register des Itanium                                 |

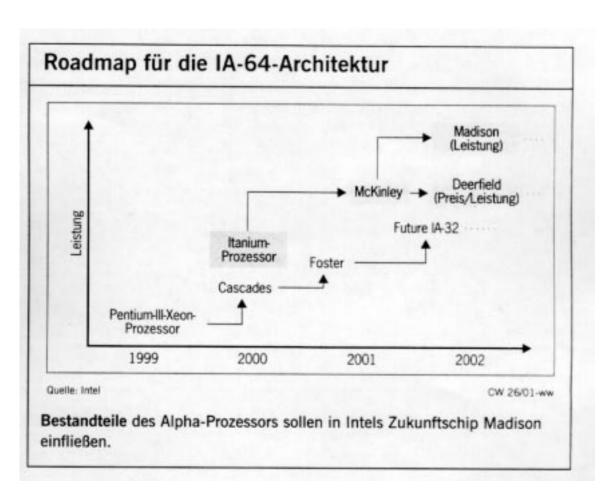

| 1.38 | Roadmap IA64                                         |

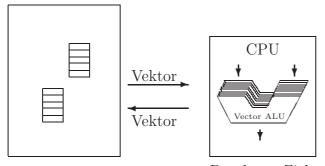

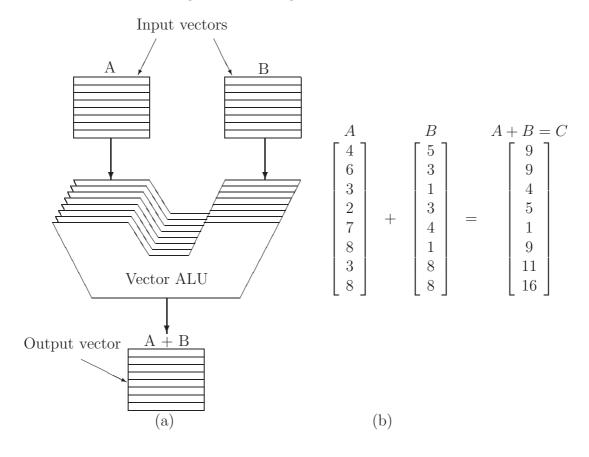

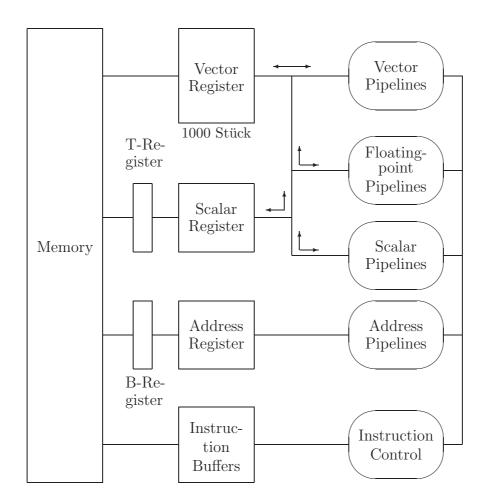

| 2.1  | Verarbeitungseinheit: Vektor von Worten              |

| 2.2  | Vektorregeister und Vektoralu                        |

| 2.3  | Rechnerstruktur eines Cray-1-Rechners                |

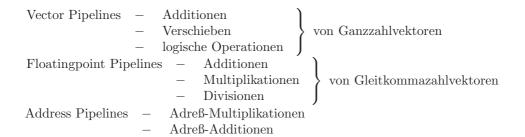

| 2.4  | Die Register und Funktionseinheiten einer Cray-1 104 |

| 2.5  | CRAY-2 (Juni 1985)                                   |

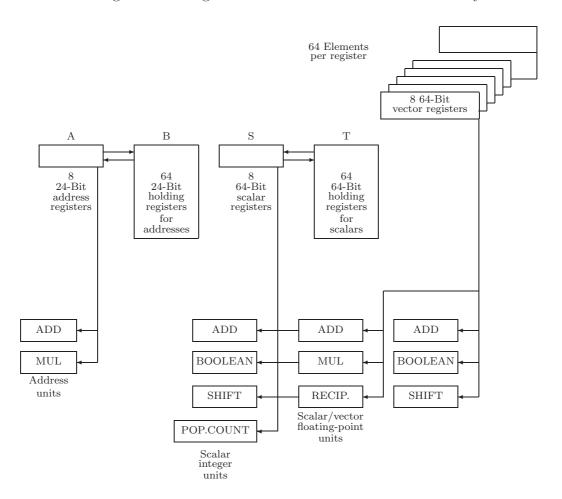

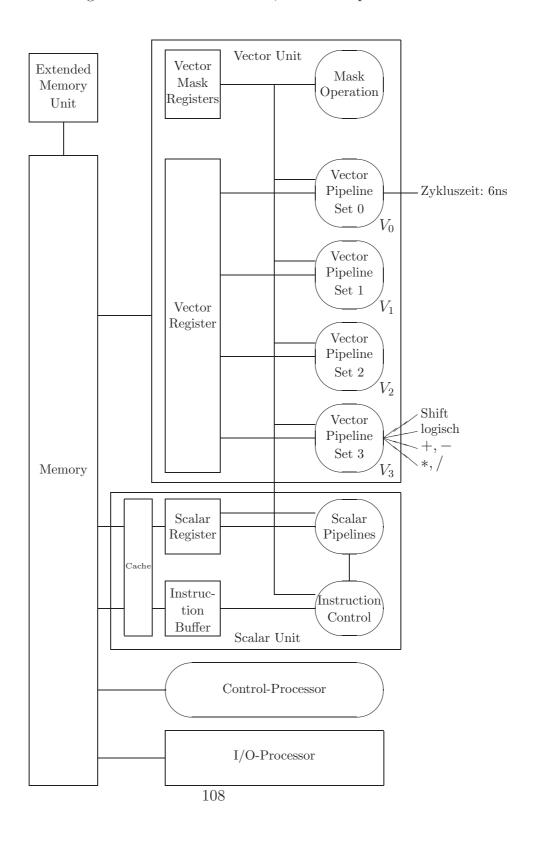

| 2.6  | NEC-SX2 SIMD, mehrere Pipelines 108                  |

| 2.7  | Systemarchitektur und Datendurchsatz                 |

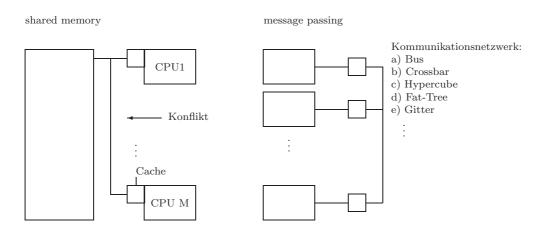

| 2.8  | "shared memory" und "message passing"                |

## Tabellenverzeichnis

| 1.1  | Zeittafel zur Entwicklung der Computertechnik                | 4           |

|------|--------------------------------------------------------------|-------------|

| 1.2  | Merkmale der 1. bis 3. Computergeneration                    | 13          |

| 1.3  | ASCII-Code                                                   | 22          |

| 1.4  | ISO-Austauschtabelle                                         | 22          |

| 1.5  | PC-8 Zeichensatz                                             | 23          |

| 1.6  | Zeichensatz für Windows 3.x                                  | 24          |

| 1.7  | ISO-8859 Latin 1(ECMA-94 Latin 1) Zeichensatz                | 25          |

| 1.8  | nationale ISO8859-Varianten                                  | 25          |

| 1.9  | UNICODE Version 1.0, Character Blocks 0000-00FF              | 28          |

| 1.10 | Weitere Zeichenbereiche                                      | 29          |

| 1.11 | UNICODE to Adobe Standard Mappings                           | 31          |

| 1.12 | The UNICODE to SGML (ISO DIS 6862.2) Mappings                | 32          |

| 1.13 | UNICODE to Macintosh Mappings                                | 33          |

| 1.14 | Analyse typischer Computeranwendungen auf ihre Instruktionst | ypen hin 45 |

| 1.15 | Von CISC zu RISC                                             | 48          |

| 1.16 | Unterscheidungsmerkmale CISC/RISC                            | 49          |

| 1.17 | RISC-CPUs im Vergleich zu Intel 80x86-CPUs                   | 52          |

| 1.18 | 64 Bit RISC-CPUs                                             | 53          |

| 1.19 | PC-Bussysteme und Durchsatzraten                             | 53          |

| 1.20 | RISC PC-CPUs: PowerPC (Apple und IBM)                        | 53          |

|      | CISC PC-CPUs: i80x86                                         |             |

| 1.22 | CISC PC-CPUs: i80x86 (Forts.)                                | 55          |

| 1.23 | Marktallianzen im RISC-Bereich                               | 58          |

| 1.24 | Anzahl der Register-Fenster und Integer-Zyklen pro Anweisung | 77          |

| 1.25 | "floating point"-Zyklen pro Anweisung                        | 78          |

| 2.1  | Klassifikation von Mehrprozessorsystemen                     |             |

| 2.2  | Speicher bei Mehrprozessorsystemen                           | 112         |

## Literatur

- Internet (siehe Links in dieser Materialsammlung).

- Duden Informatik, Ausgabe für das Studium, BI, Mannheim.

- A. S. Tanenbaum: Structured Computer Organization, Prentice-Hall.

- W. Stallings: Computer Organization and Architecture, Prentice-Hall.

## Kapitel 1

## Rechnerarchitekturen

Vom (mechanischen) Spezialgerät zum Universalrechner

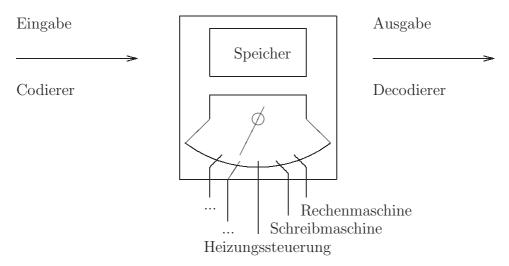

#### Im Gegensatz

- zur mechanischen Kurbel-Rechenmaschine,

- zur Schreibmaschine,

- zum Heizungsthermostat,

- zur Programmautomatik einer Waschmaschine

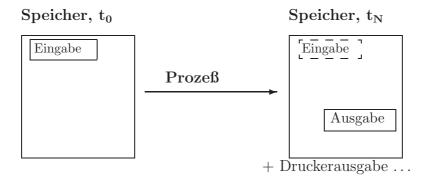

ist ein *Computer* ein universell einsetzbares Gerät zur Verarbeitung von Daten (Rechnen, Datenverarbeitung (DVA), Bereitstellung von Informationen). Diese Universalität wird dadurch erreicht, daß

- die Informationen einheitlich als binäre Daten (0/1-Informationen, Spannung da/nicht da) codiert werden (Ein-/Ausgabe),

- nur kurzzeitig verfügbare Daten in ihrer binären Codierung zwischengespeichert werden (Speicher)

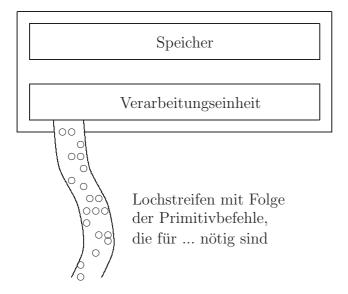

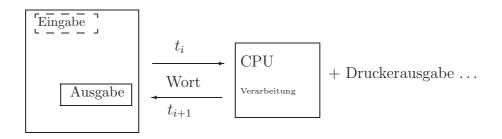

und eine *universelle* Binärdatenverarbeitungseinheit durch *Umschaltung* für fast alle denk- und lösbaren Informationsverarbeitungsaufgaben eingesetzt werden kann. Natürlich wird in der folgenden Abbildung keine volle Uni-

versalität erreicht; lediglich eine durch Schalterstellung definierbare 1 aus N Spezialauswahl ist realisiert. Sieht man jedoch eine große Anzahl von die Daten nur gering ändernden Spezialmaschinen, sogenannte Primitivbefehle oder Maschinenbefehle vor, und baut aus sequentieller Aneinanderreihung solcher Befehle den gewünschten Effekt nach und nach auf, so ist die erstrebte Universalität erreicht. Erkennt man nun schließlich, daß die benötigten

Sequenzen von Primitivbefehlen auch nur eine spezielle Art von Information sind, die deshalb — wie die Ein- und Ausgabedaten — ebenfalls codiert

im Speicher abgelegt werden können, so haben wir den prinzipiellen Aufbau eines Computers entwickelt:

Um beliebige Programme in den Computer hineinzubekommen und dann ablaufen lassen zu können, ist ein Verwaltungsprogramm, das Betriebssystem nötig, das den Computer erst benutzbar macht. Dies ist entweder in nicht-flüchtigem Speicher (ROM = read only memory, Inhalt bleibt auch in ausgeschaltetem Zustand erhalten) fest eingebaut oder wird von einer Festplatte, einem Magnetband, ... mit Hilfe des im ROM fest eingebauten Urladers oder Monitorprogramms geladen.

**Aufgabe 1.1** Diskutieren Sie die Vor- und Nachteile eines Betriebssystems im ROM und eines von Platte geladenen Betriebssystems.

Tabelle 1.1: Zeittafel zur Entwicklung der Computertechnik

| 1833        | Charles Babbage (1792-1871), Professor an der Universität Cambridge                 |

|-------------|-------------------------------------------------------------------------------------|

|             | (Großbritannien), entwirft und baut einen programmgesteuerten mechani-              |

|             | schen Rechenautomaten, die Analytical engine. Sie enthält ein 4-Spezies-            |

|             | Rechenwerk, 1000 Zahlenspeicher, Lochkartensteuerung und Ergebnis-                  |

|             | druckwerk (nicht vollendet).                                                        |

| 1941        | Vorführung des ersten arbeitsfähigen programmgesteuerten Rechenautoma-              |

|             | ten ZUSE Z3 in Relaistechnik durch Konrad Zuse (geb. 1910)                          |

| 1944        | Inbetriebnahme des programmgesteuerten elektromechanischen Rechenau-                |

|             | tomaten Mark 1 von Howard H. Aiken (1900-1973).                                     |

| 1944/46     | Formulierung der Prinzipien des von-Neumann-Computers (John von                     |

|             | NEUMANN (1903-1975). Realisiert erstmals mit der EDVAC (1952/53)                    |

| 1946        | Inbetriebnahme des ENIAC, des ersten Computers mit Elektronenröhren                 |

|             | durch John P. Eckert (geb. 1919) und John W. Mauchley (1907-                        |

|             | 1980). Beginn der Epoche der elektronischen Computer.                               |

| 1951        | Beginn der Serienproduktion elektronischer Computer mit der Anlage                  |

|             | UNIVAC I der Firma Remington Rand. Beginn der 2. Computergenera-                    |

|             | tion.                                                                               |

| 1955        | Erster Computer mit Transistoren: TRADIC (Bell. Labor.)                             |

| um $1965$   | Computer-Familie IBM/360. Beginn der 3. Computergeneration. Der Be-                 |

|             | griff Rechnerarchitektur wird erstmals verwendet.                                   |

| um $1965$   | Minirechner PDP-8 (Digital Equipment Corp.). Kleinere Rechner entstehen             |

|             | neben den Mainframes.                                                               |

| 1969        | Pilotprojekt Weitverkehrsrechnernetz ARPANET (USA) in Betrieb genom-                |

|             | men.                                                                                |

| 1971        | 4-Bit-Mikroprozessoren i4004 der Firma INTEL Corp. Beginn der Mikro-                |

|             | prozessorära. Rascher Übergang zu 8-Bit-Mikroprozessoren.                           |

| 1975 - 1980 | Personalcomputer auf Mikroprozessorbasis und die Software dafür werden              |

|             | zu Massenartikeln. Beginn der 4. Computergeneration.                                |

| um 1978     | Erste Installationen lokaler Rechnernetze.                                          |

| 1978-1980   | 16-Bit-Mikroprozessoren kommen auf den Markt.                                       |

| 1979        | Standardvorschlag der ISO $\gg Reference\ model\ of\ open\ system\ interconnection$ |

|             | tions≪ für Rechnernetze.                                                            |

| 1981-1985   | Personalcomputer mit 16-Bit-Mikroprozessoren werden marktbestimmend;                |

|             | insbesondere PC XT und AT von IBM und Kompatible dazu sowie das                     |

|             | Betriebssystem MS-DOS der Firma Microsoft.                                          |

| ab 1988     | Personalcomputer mit 32-Bit-Mikroprozessoren kommen auf den Markt                   |

|             | und lösen im Verlauf einiger Jahre die 16-Bit-Systeme ab.                           |

| ab 1996     | Workstations mit 64-Bit-Mikroprozessoren                                            |

Quelle: D.Werner (Hrsg.): Taschenbuch der Informatik; Fachbuchverlag Leipzig,  $1995\,$

Abbildung 1.1: Computersystem

## Das BIOS

Das BIOS (= Basic Input Output System) ist der in Intel-basierten Computersystemen im ROM vorhandene Betriebssystemteil, der eng mit dem Motherboard des Rechners verbunden ist:

- BIOS: http://www.qvctc.commnet.edu/classes/csc277/bios.html

- Der PC-Bootvorgang: http://www.qvctc.commnet.edu/classes/csc277/boot.html

- Motherboards/Mainboards: http://www.computerhope.com/network/mboard.htm

- BIOS-Versionen: etwa in http://www.heise.de/newsticker/data/jow-19.05.01-000/ ...

Abbildung 1.2: Der ZUSE Z3 von Konrad Zuse

## Das BIOS-Setup

Das BIOS-Setup erlaubt das Einstellen der Systemkonfiguration:

- Anzeige der vorhandenen Hardware

- Setzen von Datum und Uhrzeit der Hardware-Uhr

- (früher:) Einstellung der Festplattengeometrie (Anzahl der Zylinder, der Spuren, der Sektoren)

- Auswahl der Bootreihenfolge (Platte/n, Diskette, CDROM, USB-Speicherkarte, NIC (Network), ...)

- Konfiguration des Bootvorganges: voller/minimaler POST, Boot-CPU-Geschwindigkeit, ...

- Konfiguration der Schnittstellen (parallele/serielle/Infrarot-/...)

- Konfiguration von Tastatur (Typ, USB-Emulation, ...) und Maus (Typ, bei Laptops: Touchpad parallel, ...)

- Konfiguration der Videokarten (intern/extern/...)

- Auswahl der Prozessorgeschwindigkeit, enable/disable SpeedStep-Technology

- Anzeige des Akkustatus

- Konfiguration des Stromsparmodus/Powermanagements (für Laptops): getrennt für Netzbetrieb/Akkubetrieb: Abschaltzeiten für Videosignal, Festplatte, ...; Start des Suspend-/Hybernate-Modus; ...

- An/Aus von internem/extenem Modem, Netzwerk, ...

- Wakeup on Modem/LAN, Autoboot zu Uhrzeit, ...

- Konfiguration von Bluetooth, wireless LAN, ...

- Konfiguration des Anschlusses an eine Docking-Station

- Vereinbarung von Systempasswörtern: Master, Admin, Festplatten, ...

- ...

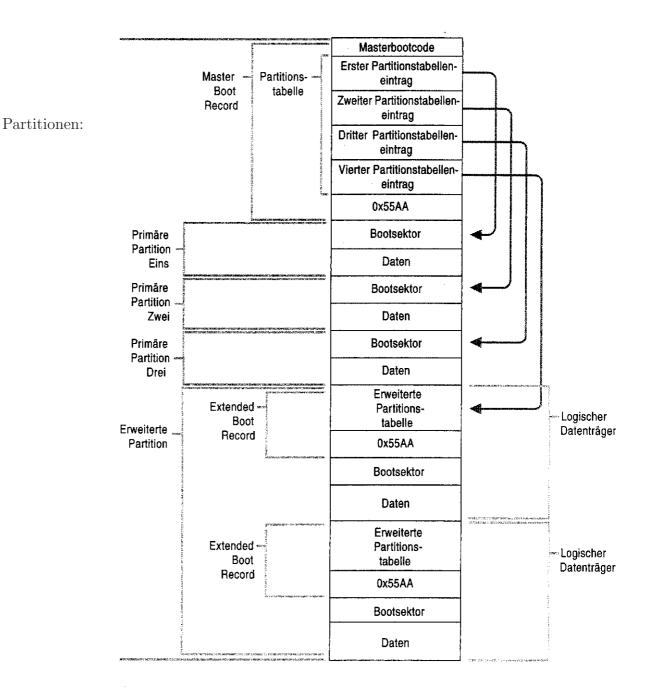

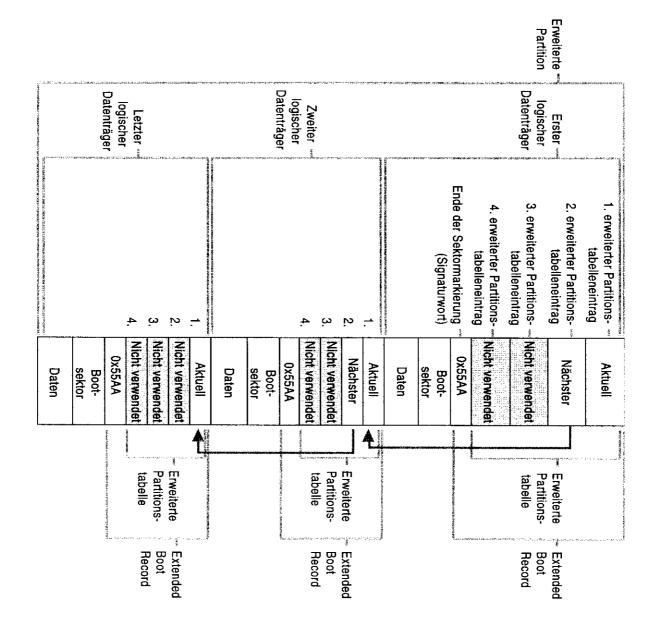

## Festplatten-Partitionierung

Für einige Zwecke sollte man eine Festplatte in mehrere "logische" Festplatten unterteilen; sie sieht dann dem Betriebssystem gegenüber wie mehrere ("physikalisch" vorhandene) Festplatten aus:

- "Vorspiegelung" mehrerer kleinerer Festplatten, wenn die Gesamtkapazität sonst für das Betriebssystem/Dateisystem unbrauchbar groß ist (FAT16-Dateisysteme konnten zum Beispiel nur maximal 2 GB groß sein).

- Gleichzeitige Installierung mehrerer Betriebssysteme auf einer Festplatte.

- Logische Trennung der Bereiche einer Platte, die zum Beispiel das Betriebssystem (inklusive Swapping-Bereich), die Anwenderprogramme und die Datenbereiche der einzelnen Benutzer (bei Terminalservern) enthalten.

- Logische Trennung von Bereichen für das Betriebssystem, für die Loggingdatenbereiche des Betriebssystems, Temporärbereiche (wie zum Beispiel 800 MB für das Image einer CD bzw. 5 GB für ein DVD-Image), . . .

- Anlegen einer gemeinsamen Daten-Partition (zum Beispiel FAT) zum Datentausch zwischen verschiedenen installierten Betriebssystemen.

- Anlegen einer dediziert nur zum Swapping benutzten Partition.

- Einrichten einer temporären Scratch-Partition.

- •

Man nennt solche "logischen" Festplatten Partitionen. Eine Festplatte wird für die genannten Zwecke partitioniert.

# bootini

[boot loader]

timeout=30

default=multi(0)disk(0)rdisk(0)partition(5)\wINDOWS

[operating systems]

multi(0)disk(0)rdisk(0)partition(5)\wINDOWS="Microsoft Windows XP Professional"

/fastdetect

multi(0)disk(0)rdisk(0)partition(1)\wINNT="Microsoft Windows 2000 Professional"

/fastdetect

Machinenzykluszahl heute: typisch

$$\frac{1}{100\,MHz} = \frac{1}{100\cdot 10^6\,s^{-1}} = 10\cdot 10^{-9}\,s = 10\,ns$$

## 1.1 Der von-Neumann-Rechner

## Die Geschichte der Computerentwicklung

Tabelle 1.2: Merkmale der 1. bis 3. Computergeneration

|                 | 1. Generation         | 2. Generation          | 3. Generation         |

|-----------------|-----------------------|------------------------|-----------------------|

|                 | ab 1951               | ab 1960                | ab 1965               |

| Basiselement    | Elektronenröhre       | Flächentransistor      | integrierter Schalt-  |

|                 |                       |                        | kreis                 |

| Arbeitsspeicher | Magnettrommel-,       | Ferritkernspeicher     | Mikroferritkernspei-  |

|                 | Umlaufspeicher        |                        | cher                  |

| Externe Spei-   | keine                 | Magnetbandspeicher,    | Magnetband-, Wech-    |

| cher            |                       | -trommelspeicher       | selplattenspeicher    |

| Ein- und Aus-   | Lochkarten- , Loch-   | wie 1. Generation      | wie 2. Generation     |

| gabegeräte      | streifengeräte, elek- | sowie Walzendrucker    | sowie Bildschirmge-   |

|                 | trische Schreibma-    |                        | räte, Datenfernüber-  |

|                 | schine                |                        | tragungsgeräte        |

| Programmie-     | Maschinencode, As-    | Assemblersprache, er-  | Assemblersprache,     |

| rung            | semblersprache        | ste problemorientierte | universelle Sprachen, |

|                 |                       | Sprachen, einfache Be- | komplexe Betriebssy-  |

|                 |                       | triebssysteme          | steme                 |

| Einsatz als     | wissenschaftlich-     | wissenschaftlich-tech- | universelle und Pro-  |

|                 | technische Rechner    | nische, kommerzielle   | zeßrechner, Einbau-   |

|                 |                       | und Prozeßrechner      | rechner               |

Quelle: D.Werner (Hrsg.): Taschenbuch der Informatik; Fachbuchverlag Leipzig,  $1995\,$

### Merkmale der 4. Generation (heute):

- VLSI-Schaltkreise

- in wenigen Jahren sich verdoppelnde Rechengeschwindigkeiten, Speichergrößen, Übertragungsgeschwindigkeiten ( $\rightarrow$  in 4 Jahren ist ein Computersystem "total" veraltet)

- Software-Entwicklungskosten höher als Hardwarekosten; wegen der schnellen Hardware-Innovationszyklen sind meist "nur" noch portable Software-Produkte schnell genug verfügbar (UNIX, TFX, ...)

- GUI's = graphical user interfaces

- Computer werden immer mehr zu IT-Geräten (Datennetzwerke)

- Laserdrucker, fotorealistischer Druck, Scanner mit 24Bit Farbtiefe

- 5. Generation: Für nach 2000 angestrebte Merkmale:

- natürlichsprachiger Umgang mit Computern

- Handschrift

- Sprache

- Multimedia, Telekonferenzen, Unterhaltung, Teleshoping, T-online, WWW, Heimarbeitsplätze, Fernkurse

- Methoden der Künstlichen Intelligenz (KI)

- Zeichen-, Bild-, Sprach-, Schrift-, Bewegungserkennung

- simultane automatische Sprachübersetzung

- Wissensverarbeitung (automatische Krankheitsdiagnose, ...)

- Nutzeridentifizierung durch Iris-Mustererkennung ...

## Blockschaltbild eines Computers

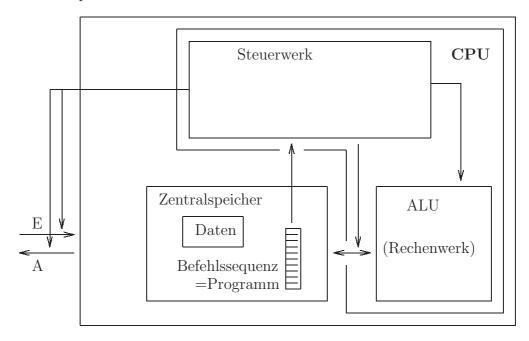

Ein von-Neumann-Rechner ist durch folgende Merkmale gekennzeichnet:

## Prinzipien:

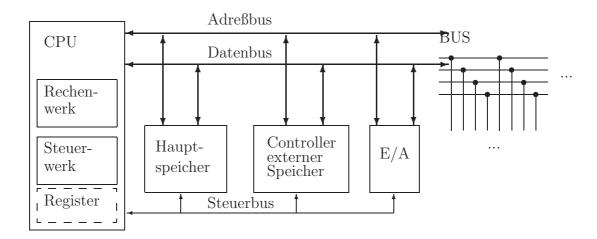

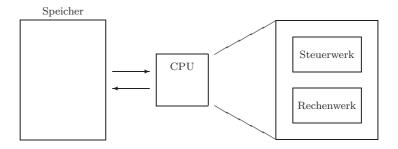

1. Computerbestandteile: CPU (= Rechenwerk und Steuerwerk), Speicher, Ein- und Ausgabewerk, Bussystem.

Abbildung 1.3: Universalrechner im Aufbau

- 2. **Universalität:** Spezialisierung nur durch von außen eingegebenes Programm.

- 3. **Programme als Daten:** Eingabedaten, Zwischen- und Endergebnisse sowie Programme werden im selben Speicher abgelegt.

- 4. Linearer Speicher: Der Speicher ist in gleichgroße Zellen, die fortlaufend numeriert sind, eingeteilt.

- 5. **Sequentielle Ausführung:** Aufeinanderfolgende Befehle eines Programms werden in aufeinanderfolgenden Speicherzellen abgelegt. Beim Programmablauf wird im allgemeinen der Befehlszähler fortlaufend inkrementiert.

- 6. **Sprünge:** Sprungbefehle ermöglichen ein Durchbrechen der linearen Ausführungsreihenfolge.

- 7. **Zusätzliche Primitiva:** Datentransferbefehle, arithmetische Operationen, logische und Vergleichsoperationen, (heute auch: Graphik- und Multimediabefehle); unmittelbare, direkte, indizierte, relative, . . . Adressierung.

- 8. Binäre Codierung: Daten (Befehle, Adressen, Operanden) werden binär codiert. Geeignete Schaltwerke (Decodierer) sorgen für die richtige Entschlüsselung.

Aufgabe: Informieren Sie sich mit Hilfe von

http://tech-www.informatik.uni-hamburg.de/applets/baukasten/DA/VNR\_Simulation\_1.html über die internen Vorgänge beim Programmablauf in einem von-Neumann-Rechner.

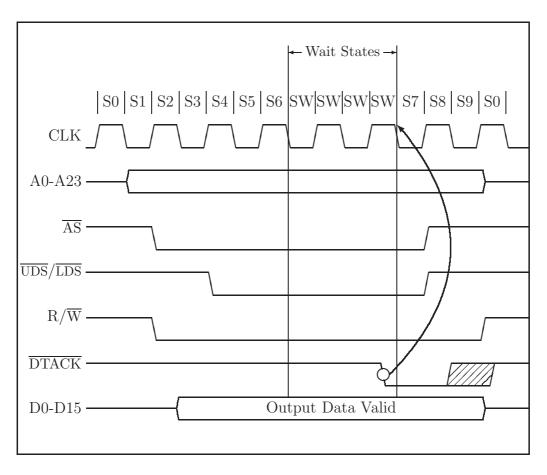

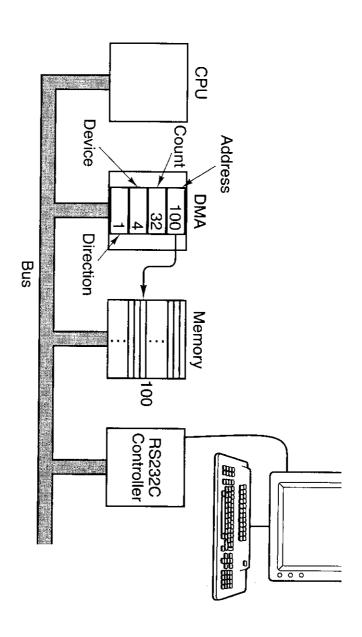

Beim geschilderten Computeraufbaustellt sich die Frage, wann welche Systemeinheit welche Bus-Leitungen benutzen darf. Dies wird durch den Controller (CPU oder DMA-Chip) mittels der *Handshake-Steuerbus-Leitungen* gemäß Abbildung 1.4 geregelt.

Abbildung 1.4: "circuit switched" Datentransfer

Aufgabe 1.2 Diskutiere: write Daten von Datenbus D0-D15 in die Speicherzelle mit der auf A0-A23 anliegenden Adresse.

#### Bemerkungen:

• Signalnamen:

| CLK                                                | = | clock                     |

|----------------------------------------------------|---|---------------------------|

| A0-A23                                             | = | address bus               |

| $\overline{\mathrm{AS}}$                           | = | address strobe            |

| $R/\overline{W}$                                   | = | read/write                |

| $\overline{\mathrm{UDS}}, \overline{\mathrm{LDS}}$ | = | upper/lower data strobe   |

| D0-D15                                             | = | data bus                  |

| DTACK                                              | = | data transfer acknowledge |

• strobe = Gültigkeitssignal für z.B. die Daten auf dem Adreßbus

#### Problem:

• circuit switched: Der Bus blockiert, bis die anstehende Operation ausgeführt ist: wait states

#### Alternative:

• packet switched: Jeder Datentransfer wird in kleine Pakete zerlegt, die jeweils deie Adresse ihres Ziels enthalten. Diese werden nacheinander nichtblockierend auf den Bus geschickt. Dadurch kann eine weitere CPU (ein weiterer Thread) schon wieder Daten transferieren, obwohl die erste CPU ihren Transfer noch nicht abgeschlossen hat.

CSMA/CD = carrier sense multiple access / collison detect

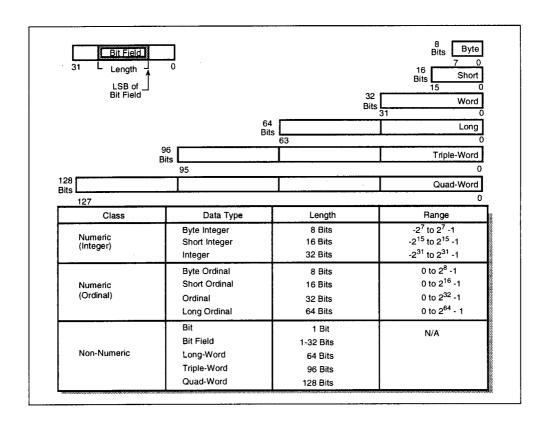

Bemerkung: Speicherinhalte werden je nach "Datentyp" unterschiedlich interpretiert

Numerische Datentypen:

Abbildung 1.5: Datentypen

## Nichtnumerische Datentypen:

Der ASCII-Code (American Standard Code for Information Interchange) ist auch heute noch Grundlage vieler Zeichencodes.

| 00 | NUL | 01 | SOH | 02 | STX          | 03 | ETX             | 04 | EOT          | 05 | ENQ                 | 06 | ACK          | 07 | BEL |

|----|-----|----|-----|----|--------------|----|-----------------|----|--------------|----|---------------------|----|--------------|----|-----|

| 08 | BS  | 09 | HT  | 0A | NL           | 0B | VT              | 0C | NP           | 0D | $\operatorname{CR}$ | 0E | SO           | 0F | SI  |

| 10 | DLE | 11 | DC1 | 12 | DC2          | 13 | DC3             | 14 | DC4          | 15 | NAK                 | 16 | SYN          | 17 | ETB |

| 18 | CAN | 19 | EM  | 1A | SUB          | 1B | ESC             | 1C | FS           | 1D | GS                  | 1E | RS           | 1F | US  |

| 20 | SP  | 21 | !   | 22 | "            | 23 | #               | 24 | \$           | 25 | %                   | 26 | &            | 27 | ,   |

| 28 | (   | 29 | )   | 2A | *            | 2B | +               | 2C | ,            | 2D | -                   | 2E |              | 2F | /   |

| 30 | 0   | 31 | 1   | 32 | 2            | 33 | 3               | 34 | 4            | 35 | 5                   | 36 | 6            | 37 | 7   |

| 38 | 8   | 39 | 9   | 3A | :            | 3В | ;               | 3C | <            | 3D | =                   | 3E | >            | 3F | ?   |

| 40 | @   | 41 | A   | 42 | В            | 43 | $^{\mathrm{C}}$ | 44 | D            | 45 | $\mathbf{E}$        | 46 | $\mathbf{F}$ | 47 | G   |

| 48 | Η   | 49 | I   | 4A | J            | 4B | K               | 4C | ${ m L}$     | 4D | ${ m M}$            | 4E | N            | 4F | Ο   |

| 50 | Р   | 51 | Q   | 52 | $\mathbf{R}$ | 53 | $\mathbf{S}$    | 54 | ${ m T}$     | 55 | U                   | 56 | V            | 57 | W   |

| 58 | X   | 59 | Y   | 5A | $\mathbf{Z}$ | 5B | [               | 5C | \            | 5D | ]                   | 5E | ^            | 5F | _   |

| 60 | `   | 61 | a   | 62 | b            | 63 | $^{\mathrm{c}}$ | 64 | d            | 65 | e                   | 66 | f            | 67 | g   |

| 68 | h   | 69 | i   | 6A | j            | 6B | k               | 6C | 1            | 6D | $\mathbf{m}$        | 6E | n            | 6F | О   |

| 70 | p   | 71 | q   | 72 | r            | 73 | $\mathbf{s}$    | 74 | $\mathbf{t}$ | 75 | u                   | 76 | $\mathbf{v}$ | 77 | w   |

| 78 | X   | 79 | У   | 7A | $\mathbf{Z}$ | 7B | {               | 7C |              | 7D | }                   | 7E | ~            | 7F | DEL |

Tabelle 1.3: ASCII-Code

Da sieben Bit, also 128 Zeichen nicht für landesspezifische Sonderzeichen ausreichten, entstanden die landesspezifischen Varianten durch Zeichenersetzung (vgl. Tabelle 1.4).

| ISO | Zeichensatz     | Dezimalform |    |    |    |    |    |    |    |       |     |     |     |     |

|-----|-----------------|-------------|----|----|----|----|----|----|----|-------|-----|-----|-----|-----|

| Nr. | Zeienensauz     | ID          | 35 | 36 | 64 | 91 | 92 | 93 | 94 | 96    | 123 | 124 | 125 | 126 |

| 6   | ANSI ASCII      | 0U          | #  | \$ | @  | [  | \  |    | ^  | `     | {   |     | }   | ~   |

| 11  | Schweden: Namen | 0S          | #  |    | É  | Ä  | Ö  | Å  | Ü  | `     | ä   | ö   | å   | ü   |

| 10  | Schweden        | 3S          | #  |    | @  | Ä  | Ö  | Å  | ^  | `     | ä   | ö   | å   |     |

| 17  | Spanien         | 2S          | £  | \$ | §  | i  | Ñ  | į  | ^  | `     | 0   | ñ   | ç   | ~   |

| 69  | Frankreich      | 1F          | £  | \$ | à  | 0  | ç  | §  | ^  | $\mu$ | é   | ù   | è   |     |

| 21  | Deutschland     | 1G          | #  | \$ | §  | Ä  | Ö  | Ü  | ^  | `     | ä   | ö   | ü   | ß   |

| 4   | Großbritannien  | 1E          | £  | \$ | @  | [  | \  | ]  | ^  | `     | {   |     | }   |     |

| 16  | Portugal        | 4S          | #  | \$ | §  | Ã  | Ç  | Õ  | ^  | `     | ã   | ç   | õ   | 0   |

| 60  | Norwegen 1      | 0D          | #  | \$ | @  | Æ  | Ø  | Å  | ^  | `     | æ   | Ø   | å   |     |

| 61  | Norwegen 2      | 1D          | §  | \$ | @  | Æ  | Ø  | Å  | ^  | `     | æ   | Ø   | å   |     |

| 2   | IRV             |             | #  |    | @  |    | \  |    | ^  | `     | {   |     | }   |     |

| 15  | Italien         | 0I          | £  | \$ | §  | 0  | ç  | é  | ^  | `     | à   | ò   | è   | ì   |

Tabelle 1.4: ISO-Austauschtabelle

Alternativ wurden acht Bit (256 Zeichen) für landesspezifische Sonderzeichen, mathematische Symbole, graphische Symbole zum Tabellendruck bzw. für Sonderzwecke (Spiele, ...) besetzt, etwa im Industriestandard PC-8 Zeichensatz (Tabelle 1.5)<sup>1</sup>.

|         |                   |    | 0  | @  | Р  | (   | р            | Ç   | É   | á   |          |          |     | α          | =         |

|---------|-------------------|----|----|----|----|-----|--------------|-----|-----|-----|----------|----------|-----|------------|-----------|

| 0       | 16                | 32 | 48 | 64 | 80 | 96  | 112          | 128 | 144 | 160 | 176      | 192      | 208 | 224        | 240       |

|         |                   | !  | 1  | Α  | Q  | a   | q            | ü   | æ   | í   |          |          |     | ß          | ±         |

| 1       | 17                | 33 | 49 | 65 | 81 | 97  | 113          | 129 | 145 | 161 | 177      | 193      | 209 | 225        | 241       |

|         | $\uparrow$        | "  | 2  | В  | R  | b   | r            | é   | Æ   | ó   |          | Т        |     | Γ          | $\geq$    |

| 2       | 18                | 34 | 50 | 66 | 81 | 98  | 114          | 130 | 146 | 162 | 178      | 194      | 210 | 226        | 242       |

|         | !!                | #  | 3  | С  | S  | С   | S            | â   | ô   | ú   |          | $\vdash$ |     | $\pi$      | $\leq$    |

| 3       | 19                | 35 | 51 | 67 | 82 | 99  | 115          | 131 | 147 | 163 | 179      | 195      | 211 | 227        | 243       |

|         | ¶                 | \$ | 4  | D  | Т  | d   | t            | ä   | ö   | ñ   | $\dashv$ |          |     | $\sum$     |           |

| 4       | 20                | 36 | 52 | 68 | 83 | 100 | 116          | 132 | 148 | 164 | 180      | 196      | 212 | 228        | 244       |

| *       | §                 | %  | 5  | Ε  | U  | е   | u            | à   | ò   | Ñ   |          |          |     | $\sigma$   |           |

| 5       | 21                | 37 | 53 | 69 | 84 | 101 | 117          | 133 | 149 | 165 | 181      | 197      | 213 | 229        | 245       |

| •       |                   | &  | 6  | F  | V  | f   | V            | å   | û   | a   |          |          |     | $\mu$      | ÷         |

| 6       | 22                | 38 | 54 | 70 | 85 | 102 | 118          | 134 | 150 | 166 | 182      | 198      | 214 | 230        | 246       |

|         |                   | ,  | 7  | G  | W  | g   | W            | ç   | ù   | 0   |          |          |     | au         | $\approx$ |

| 7       | 23                | 39 | 55 | 71 | 86 | 103 | 119          | 135 | 151 | 167 | 183      | 199      | 215 | 231        | 247       |

|         | 1                 | (  | 8  | Η  | X  | h   | X            | ê   | ÿ   | i   |          |          |     | Φ          | 0         |

| 8       | 24                | 40 | 56 | 72 | 87 | 104 | 120          | 136 | 152 | 168 | 184      | 200      | 216 | 232        | 248       |

| $\circ$ | ↓                 | )  | 9  | I  | Y  | i   | У            | ë   | Ö   |     |          |          |     | Θ          | •         |

| 9       | 25                | 41 | 57 | 73 | 88 | 105 | 121          | 137 | 153 | 169 | 185      | 201      | 217 | 233        | 249       |

|         | $\rightarrow$     | *  | :  | J  | Z  | j   | $\mathbf{z}$ | è   | Ü   | _   |          |          |     | Ω          | •         |

| 10      | 26                | 42 | 58 | 74 | 89 | 106 | 122          | 138 | 154 | 170 | 186      | 202      | 218 | 234        | 250       |

|         | $\leftarrow$      | +  | ;  | K  |    | k   | {            | ï   | Ç   |     |          |          |     | δ          | $\sqrt{}$ |

| 11      | 27                | 43 | 59 | 75 | 90 | 107 | 123          | 139 | 155 | 171 | 187      | 203      | 219 | 235        | 251<br>n  |

|         |                   | ,  | <  | L  | \  | 1   |              | î   | £   |     |          |          |     | $\infty$   | 71        |

| 12      | 28                | 44 | 60 | 76 | 91 | 108 | 124          | 140 | 156 | 172 | 188      | 204      | 220 | 236        | 252       |

|         | $\leftrightarrow$ | -  | =  | М  |    | m   | }            | ì   |     | i   |          |          |     | $\phi$     |           |

| 13      | 29                | 45 | 61 | 77 | 92 | 109 | 125          | 141 | 157 | 173 | 189      | 205      | 221 | 237        | 253       |

|         |                   |    | >  | Ν  | ^  | n   | ~            | Ä   | Pt  | «   |          |          |     | $\epsilon$ |           |

| 14      | 30                | 46 | 62 | 78 | 93 | 110 | 126          | 142 | 158 | 174 | 190      | 206      | 222 | 238        | 254       |

|         |                   | /  | ?  | О  | _  | О   |              | Å   | f   | >>  |          |          |     | $\cap$     |           |

| 15      | 31                | 47 | 63 | 79 | 94 | 111 | 127          | 143 | 159 | 175 | 191      | 207      | 223 | 239        | 255       |

Tabelle 1.5: PC-8 Zeichensatz

¹In dieser – wie auch in einigen der folgenden Tabellen – sind leere Codestellen entweder unbesetzt oder wegen Problemen beim Satz der entsprechenden Zeichen in diesem Skript freigelassen worden.

In Windows 3.x wurden jedoch andere Codierungen genutzt (Tabelle 1.6). Der inzwischen verabschiedete Standard der *International Standardization*

| NUL |     |    | 0  | @  | Р  | `   | р            |     |     |        | 0             | À   |     | à   |     |

|-----|-----|----|----|----|----|-----|--------------|-----|-----|--------|---------------|-----|-----|-----|-----|

| 0   | 16  | 32 | 48 | 64 | 80 | 96  | 112          | 128 | 144 | 160    | 176           | 192 | 208 | 224 | 240 |

|     |     | !  | 1  | A  | Q  | a   | q            |     | (   | i      | ±             | Á   | Ñ   | á   | ñ   |

| 1   | 17  | 33 | 49 | 65 | 81 | 97  | 113          | 129 | 145 | 161    | 177           | 193 | 209 | 225 | 241 |

|     |     | "  | 2  | В  | R  | b   | r            |     | ,   | ç      | 2             | Â   | Ò   | â   | ò   |

| 2   | 18  | 34 | 50 | 66 | 81 | 98  | 114          | 130 | 146 | 162    | 178           | 194 | 210 | 226 | 242 |

|     |     | #  | 3  | С  | S  | С   | s            |     |     | £      | 3             | Ã   | Ó   | ã   | ó   |

| 3   | 19  | 35 | 51 | 67 | 82 | 99  | 115          | 131 | 147 | 163    | 179           | 195 | 211 | 227 | 243 |

|     |     | \$ | 4  | D  | Т  | d   | t            |     |     |        | ,             | Ä   | Ô   | ä   | ô   |

| 4   | 20  | 36 | 52 | 68 | 83 | 100 | 116          | 132 | 148 | 164    | 180           | 196 | 212 | 228 | 244 |

|     |     | %  | 5  | Ε  | U  | е   | u            |     |     |        | $\mu$         | Å   | Õ   | å   | õ   |

| 5   | 21  | 37 | 53 | 69 | 84 | 101 | 117          | 133 | 149 | 165    | 181           | 197 | 213 | 229 | 245 |

|     |     | &  | 6  | F  | V  | f   | V            |     |     |        | $\P$          | Æ   | Ö   | æ   | ö   |

| 6   | 22  | 38 | 54 | 70 | 85 | 102 | 118          | 134 | 150 | 166    | 182           | 198 | 214 | 230 | 246 |

| BEL |     | /  | 7  | G  | W  | g   | W            |     |     | §      |               | Ç   | ×   | ç   | ÷   |

| 7   | 23  | 39 | 55 | 71 | 86 | 103 | 119          | 135 | 151 | 167    | 183           | 199 | 215 | 231 | 247 |

| BS  |     | (  | 8  | Η  | X  | h   | X            |     |     |        |               | È   | Ø   | è   | Ø   |

| 8   | 24  | 40 | 56 | 72 | 87 | 104 | 120          | 136 | 152 | 168    | 184           | 200 | 216 | 232 | 248 |

| HT  |     | )  | 9  | Ι  | Y  | i   | У            |     |     | ©      | 1             | É   | Ù   | é   | ù   |

| 9   | 25  | 41 | 57 | 73 | 88 | 105 | 121          | 137 | 153 | 169    | 185           | 201 | 217 | 233 | 249 |

| LF  |     | *  | :  | J  | Z  | j   | $\mathbf{z}$ |     |     | a      | 0             | E   | Ü   | ê   | ú   |

| 10  | 26  | 42 | 58 | 74 | 89 | 106 | 122          | 138 | 154 | 170    | 186           | 202 | 218 | 234 | 250 |

| VT  | ESC | +  | ;  | K  | [  | k   | {            |     |     | «      | >>            | Ë   | Û   | ë   | û   |

| 11  | 27  | 43 | 59 | 75 | 90 | 107 | 123          | 139 | 155 | 171    | 187           | 203 | 219 | 235 | 251 |

| FF  |     | ,  | <  | L  | \  | 1   |              |     |     | $\neg$ | $\frac{1}{4}$ | Ì   | Û   | ì   | ü   |

| 12  | 28  | 44 | 60 | 76 | 91 | 108 | 124          | 140 | 156 | 172    | 188           | 204 | 220 | 236 | 252 |

| CR  |     | -  | =  | Μ  | ]  | m   | }            |     |     | -      | $\frac{1}{2}$ | Í   | Ý   | í   | ý   |

| 13  | 29  | 45 | 61 | 77 | 92 | 109 | 125          | 141 | 157 | 173    | 189           | 205 | 221 | 237 | 253 |

| SO  |     |    | >  | N  | ^  | n   | ~            |     |     |        | $\frac{3}{4}$ | I   |     | î   |     |

| 14  | 30  | 46 | 62 | 78 | 93 | 110 | 126          | 142 | 158 | 174    | 190           | 206 | 222 | 238 | 254 |

| SI  |     | /  | ?  | Ο  | _  | О   |              |     |     | _      | į             | Ï   | ß   | ï   | ÿ   |

| 15  | 31  | 47 | 63 | 79 | 94 | 111 | 127          | 143 | 159 | 175    | 191           | 207 | 223 | 239 | 255 |

Tabelle 1.6: Zeichensatz für Windows 3.x

Organisation (ISO), der ISO-8859 Latin 1(ECMA-94 Latin 1) Zeichensatz (Tabelle 1.7) setzte sich insbesondere bei Workstations und neueren Hardund Softwareprodukten durch. Neben der Latin-1 Version existieren auch noch einige andere nationale Sonderformen des ISO 8859 Codes (vgl. Tabelle 1.8).

|    |    |    | 0  | 0  | Р  | (   | р            |     |     |     | 0             | À   |     | à   |     |

|----|----|----|----|----|----|-----|--------------|-----|-----|-----|---------------|-----|-----|-----|-----|

| 0  | 16 | 32 | 48 | 64 | 80 | 96  | 112          | 128 | 144 | 160 | 176           | 192 | 208 | 224 | 240 |

|    |    | !  | 1  | Α  | Q  | a   | q            |     |     | i   | 土             | Á   | Ñ   | á   | ñ   |

| 1  | 17 | 33 | 49 | 65 | 81 | 97  | 113          | 129 | 145 | 161 | 177           | 193 | 209 | 225 | 241 |

|    |    | "  | 2  | В  | R  | b   | r            |     |     |     | 2             | Â   | Ò   | â   | ò   |

| 2  | 18 | 34 | 50 | 66 | 81 | 98  | 114          | 130 | 146 | 162 | 178           | 194 | 210 | 226 | 242 |

|    |    | #  | 3  | С  | S  | С   | S            |     |     | £   | 3             | Ã   | Ó   | ã   | ó   |

| 3  | 19 | 35 | 51 | 67 | 82 | 99  | 115          | 131 | 147 | 163 | 179           | 195 | 211 | 227 | 243 |

|    |    | \$ | 4  | D  | Т  | d   | t            |     |     |     | ′             | Ä   | Ô   | ä   | ô   |

| 4  | 20 | 36 | 52 | 68 | 83 | 100 | 116          | 132 | 148 | 164 | 180           | 196 | 212 | 228 | 244 |

|    |    | %  | 5  | Е  | U  | е   | u            |     |     |     | $\mu$         | Å   | Õ   | å   | õ   |

| 5  | 21 | 37 | 53 | 69 | 84 | 101 | 117          | 133 | 149 | 165 | 181           | 197 | 213 | 229 | 245 |

|    |    | &  | 6  | F  | V  | f   | V            |     |     |     | $\P$          | Æ   | Ö   | æ   | ö   |

| 6  | 22 | 38 | 54 | 70 | 85 | 102 | 118          | 134 | 150 | 166 | 182           | 198 | 214 | 230 | 246 |

|    |    | ,  | 7  | G  | W  | g   | W            |     |     | §   |               | Ç   | ×   | ç   | ÷   |

| 7  | 23 | 39 | 55 | 71 | 86 | 103 | 119          | 135 | 151 | 167 | 183           | 199 | 215 | 231 | 247 |

|    |    | (  | 8  | Н  | X  | h   | X            |     |     |     |               | È   | Ø   | è   | Ø   |

| 8  | 24 | 40 | 56 | 72 | 87 | 104 | 120          | 136 | 152 | 168 | 184           | 200 | 216 | 232 | 248 |

|    |    | )  | 9  | Ι  | Y  | i   | У            |     |     | ©   | 1             | É   | Ù   | é   | ù   |

| 9  | 25 | 41 | 57 | 73 | 88 | 105 | 121          | 137 | 153 | 169 | 185           | 201 | 217 | 233 | 249 |

|    |    | *  | :  | J  | Z  | j   | $\mathbf{z}$ |     |     | a   | 0             | Ê   | Ú   | ê   | ú   |

| 10 | 26 | 42 | 58 | 74 | 89 | 106 | 122          | 138 | 154 | 170 | 186           | 202 | 218 | 234 | 250 |

|    |    | +  | ;  | K  | [  | k   | {            |     |     | «   | >>            | E   | Ü   | ë   | û   |

| 11 | 27 | 43 | 59 | 75 | 90 | 107 | 123          | 139 | 155 | 171 | 187           | 203 | 219 | 235 | 251 |

|    |    | ,  | <  | L  | \  | 1   |              |     |     | _   | $\frac{1}{4}$ | Ì   | Ü   | ì   | ü   |

| 12 | 28 | 44 | 60 | 76 | 91 | 108 | 124          | 140 | 156 | 172 | 188           | 204 | 220 | 236 | 252 |

|    |    | -  | =  | Μ  | ]  | m   | }            |     |     | -   | $\frac{1}{2}$ | I   | Ý   | í   | ý   |

| 13 | 29 | 45 | 61 | 77 | 92 | 109 | 125          | 141 | 157 | 173 | 189           | 205 | 221 | 237 | 253 |

|    |    |    | >  | N  | ^  | n   | ~            |     |     |     | $\frac{3}{4}$ | Î   |     | î   |     |

| 14 | 30 | 46 | 62 | 78 | 93 | 110 | 126          | 142 | 158 | 174 | 190           | 206 | 222 | 238 | 254 |

|    |    | /  | ?  | О  | _  | О   |              |     |     | _   | į             | Ï   | ß   | ï   | ÿ   |

| 15 | 31 | 47 | 63 | 79 | 94 | 111 | 127          | 143 | 159 | 175 | 191           | 207 | 223 | 239 | 255 |

Tabelle 1.7: ISO-8859 Latin 1<br/>(ECMA-94 Latin 1) Zeichensatz

| Code Set | Name     | Coverage                              | Approved         |

|----------|----------|---------------------------------------|------------------|

| 8859-1   | Latin-1  | western Europe                        | 15 February 1987 |

| 8859-2   | Latin-2  | eastern Europe                        | 15 February 1987 |

| 8859-3   | Latin-3  | Maltese, Catalan, Galician, Esperanto | 15 April 1988    |

| 8859-4   | Latin-4  | Baltic and Nordic region              | 15 April 1988    |

| 8859-5   | Cyrillic | Slavic countries                      | 1 December 1988  |

| 8859-6   | Arabic   | Arab countries                        | 15 August 1987   |

| 8859-7   | Greek    | Greece                                | 15 November 1987 |

| 8859-8   | Hebrew   | Israel                                | 1 June 1988      |

| 8859-9   | Latin-5  | 8859-1 minus Iceland plus Turkey      | 15 May 1989      |

Tabelle 1.8: nationale ISO8859-Varianten

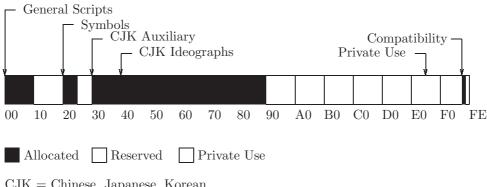

Eine weltweite Anwendbarkeit eines Zeichencodes kann erreicht werden, falls 16 Bit für die Codierung zur Verfügung stehen: UNICODE, der in neuen Programmiersprachen wie etwa JAVA schon benutzt wird.

#### Statistik der Version 1.0

CJK = Chinese, Japanese, Korean

Abbildung 1.6: Verteilung UNICODE

Die folgende Tabelle zeigt die Anteile des gesamten im UNICODE zur Verfügung stehenden Platzes, die verschiedenen Schrifttypen in der Version 1.0 bereits zugeteilt wurden:

|                     | Allocated   | Un assigned  | % Assigend |            |

|---------------------|-------------|--------------|------------|------------|

| General             | 2336        | 5856         | 29%        |            |

| Symbols             | 1290        | 2806         | 31%        |            |

| CJK symbols         | 763         | 261          | 75%        |            |

| Hangul              | 2350        | 450          | 84%        |            |

| Han Compatibility   | 268         | 4            | 99%        | (Volume 2) |

| Ideographic & other | 20733       | 22275        | 48%        | (Volume 2) |

| User Space          | 5632        | N/A          | N/A        |            |

| Compatibility Zone  | 362         | 133          | 73%        |            |

| Special             | 1           | 13           |            |            |

| FEFF                | 1           | 0            |            |            |

| FFFE, FFFF          | N/A         | 2            |            |            |

| Totals              | 2870        | 6 (assigned) |            |            |

|                     | + 5632  (ps | rivate use)  |            |            |

|                     | = 34338     | (allocated)  |            |            |

|                     | 52%         |              |            |            |

Mit noch über 30000 unbenutzten Character Positionen besitzt der UNICO-DE auch für die Zukunft noch genug Raum für weitere Expansionen.

#### Die Zukunft des UNICODES

In Zukunft wird der UNICODE Standard um weniger verbreitete und veraltete Schrifttypen erweitert. Schrifttypen dieser Art werden jedoch nicht in ihrer ursprünglichen Form eingebunden, da sich ihr Nutzen schwer einschätzen läßt. So wird bei vielen dieser Schriften eine ausführliche Diskussion nötig sein, bis ein zufriedenstellendes Codierungsschema vorliegt. Die fünf Schriftarten Ethiopian, Burmese, Khmer, Sinhala und Mongolian werden zum Standard UNICODE hinzugefügt, sobald zuverlässige Informationen über sie vorliegen. Weitere Schriftarten, die für eine mögliche Aufnahme vorgesehen sind, sind

- Inuktitut/Cree Syllabary: Das Kommunikationsministerium von Kanada untersucht Standardisierungen von verschiedenen Dialektarten, die von Cree und/oder Inuktitut gesprochen werden und sucht Codierungsschemen.

- Egyptian Hieroglyphics: Ein einheitliches Codierungsschema existiert und wird vorangetrieben.

- Korean Hangul Syllables: Eventuell werden noch weitere Korean Hangul Dialekte hinzugefügt.

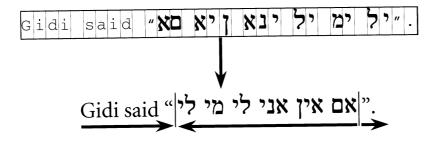

Der Unterschied zwischen der logischen Anordung von Zeichen und der Anordnung auf dem Bildschirm zeigt die Abbildung 1.7

Abbildung 1.7: Bidirectional Ordering

#### General Scripts

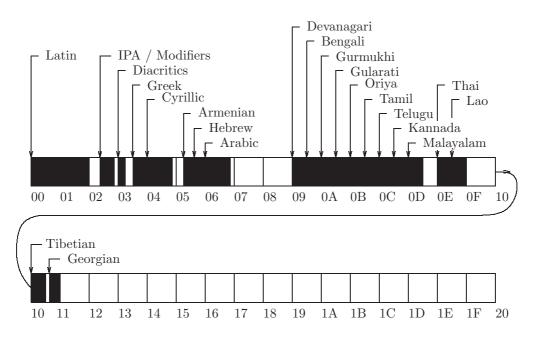

Im *General Scripts*-Bereich des UNICODEs sind alle lateinischen und nichtideographischen Schriftzeichen codiert:

Abbildung 1.8: General Scripts

| Control |     | ASCII |       |       |       |     |              | Con  | Latin 1 |        |                              |     |     |     |     |

|---------|-----|-------|-------|-------|-------|-----|--------------|------|---------|--------|------------------------------|-----|-----|-----|-----|

| 000     | 001 | 002   | 2 003 | 3 004 | 1 005 | 006 | 007          | 008  | 009     | 00A    | 00B                          | 00C | 00D | 00E | 00F |

| NUL     | DLE |       | 0     | @     | Р     | (   | р            | CTRL | CTRL    |        | 0                            | À   |     | à   |     |

| SOH     | DC1 | !     | 1     | Α     | Q     | a   | q            | CTRL | CTRL    | i      | 土                            | Á   | Ñ   | á   | ñ   |

| STX     | DC2 | 11    | 2     | В     | R     | b   | r            | CTRL | CTRL    |        | 2                            | Â   | Ò   | â   | ò   |

| ETX     | DC3 | #     | 3     | С     | S     | С   | S            | CTRL | CTRL    | £      | 3                            | Ã   | Ó   | ã   | ó   |

| EOT     | DC4 | \$    | 4     | D     | Τ     | d   | t            | CTRL | CTRL    |        | ,                            | Ä   | Ô   | ä   | ô   |

| ENQ     | NAK | %     | 5     | Ε     | U     | е   | u            | CTRL | CTRL    |        | $\mu$                        | Å   | Õ   | å   | õ   |

| ACK     | SYN | &     | 6     | F     | V     | f   | V            | CTRL | CTRL    |        | $\P$                         | Æ   | Ö   | æ   | ö   |

| BEL     | ETB | ,     | 7     | G     | W     | g   | W            | CTRL | CTRL    | §      |                              | Ç   | ×   | ç   | ÷   |

| BS      | CAN | (     | 8     | Η     | X     | h   | X            | CTRL | CTRL    |        | د                            | È   | Ø   | è   | Ø   |

| HT      | EM  | )     | 9     | Ι     | Y     | i   | У            | CTRL | CTRL    | ©      | 1                            | É   | Ù   | é   | ù   |

| LF      | SUB | *     | :     | J     | Z     | j   | $\mathbf{z}$ | CTRL | CTRL    | a      | 0                            | Ê   | Ú   | ê   | ú   |

| VT      | ESC | +     | ;     | K     | [     | k   | {            | CTRL | CTRL    | «      | >>                           | Ë   | Û   | ë   | û   |

| FF      | FS  | ,     | <     | L     | \     | 1   |              | CTRL | CTRL    | $\neg$ | $\frac{1}{4}$                | Ì   | Ü   | ì   | ü   |

| CR      | GS  | -     | =     | Μ     | ]     | m   | }            | CTRL | CTRL    | -      |                              | Í   | Ý   | í   | ý   |

| SO      | RS  |       | >     | Ν     | ^     | n   | ~            | CTRL | CTRL    |        | $\frac{1}{2} \\ \frac{3}{4}$ | Î   |     | î   |     |

| SI      | US  | /     | ?     | Ο     | _     | О   | DEL          | CTRL | CTRL    | _      | į                            | Ï   | ß   | ï   | ÿ   |

Tabelle 1.9: UNICODE Version 1.0, Character Blocks 0000-00FF

```

Zeichen für die Zeichensetzung: ,.:;", ...

2000..206F

Subscripts und Superscripts: <sup>2</sup>, <sup>3</sup>, <sup>4</sup>, ...

2070..209F

20A0..20CF

Währungssymbole: £,$, ...

diakretische Zeichen: ^{\leftarrow}, ^{\rightarrow}, \dots

20D0..20FF

2100..214F

buchstabenähnliche Zeichen: \mathcal{F}, {}^{\circ}F, \dots

Zahlen: \frac{1}{3}, I, VII, ...

2150..218F

2190..21FF

Pfeile: \uparrow, \mapsto, ...

2200..22FF

mathematische Sonderzeichen: \forall, \exists, \in, ...

verschiedene technische Sonderzeichen: #, ...

2300..23FF

2400..243F

Symbole für Control-Zeichen: NUL,ESC, ...

OCR-Zeichen

2440..245F

2460..24FF

eingerahmte alphanumerische Zeichen: ©, ...

2500..257F

Formular- und Diagrammzeichen: \vdash, \dashv, \parallel, ...

2580..259F

Blockgraphik-Zeichen

25A0..25FF

graphische Symbole

2600..26FF

verschiedene Dingbats

2700..27BF

Zapf-Dingbats

3000..303F

CJK-Symbole

3040..309F

Hiragana

30A0..30FF

Katakana

...

```

Tabelle 1.10: Weitere Zeichenbereiche

Der UNICODE stellt weitgehende Kompatibilität zu bestehenden Codes durch (verschobenes) Einfügen oder Bereitstellen von Code-Umwandlungstabellen her: 0000..007F entspricht ASCII. Für andere Codes werden UNICODE-Übersetzungstabellen bereitgestellt, z.B. für UNICODE zu SGML (Tabelle 1.12), UNICODE zu Postscript (Tabelle 1.11) oder UNICODE zu MacIntosh (Tabelle 1.13). Analoge Tabellen gibt es zur Übersetzung von UNICODE zu Microsoft Windows, zu PC Code Page Mappings (Latin, Greek,...), zu EBCDIC Code Page Mappings und weiteren.

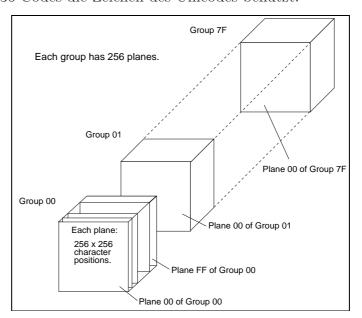

Die Notwendigkeit, Control-Codes anderer Codierungen auch verfügbar zu haben, und die Weigerung von Japan und Korea, die vereinheitlichte CJK-Codierung (die mit 19000 statt insgesamt über 31000 Codepositionen ausgekommen wäre) zu akzeptieren, führt zum 32Bit Zeichencode *ISO 10646*, der in seinen ersten 65536 Codes die Zeichen des Unicodes benutzt:

Näheres zum ISO- bzw. Unicode lese man bei

http://dns.hti.umich.edu/htistaff/pubs/1997/janete.01/,

http://www.indigo.ie/egt/standards/iso10646/bmp-today-table.html,

http://wwwinfo.cern.ch/asdoc/WWW/publications/ictp99/ictp99N2705.html

und

http://www.unicode.org/

nach. Die nun zur Verfügung stehenden 4294967296 Codes dürften voraussichtlich für eine Codierung auch der ausgefallensten (ausgestorbenen) Schriften ausreichen.

|      | ISO La        | tin1 | ZapfDB        |                  |                        |

|------|---------------|------|---------------|------------------|------------------------|

| UNIC | StdEnc        |      | Symbol        | Adobe glyph name | Unicode character name |

| 0020 | 20            | 20   | 20            | space            | SPACE                  |

| 0021 | 21            | 21   | 21            | exclam           | ECLAMATION MARK        |

| 0022 | 22            | 22   |               | quotedbl         | QUOTATION MARK         |

| 0023 | 23            | 23   | 23            | numbersign       | NUMBERSIGN             |

| 0024 | 24            | 24   |               | dollar           | DOLLAR SIGN            |

| 0025 | 25            | 25   | 25            | percent          | PERCENT SIGN           |

| 0026 | 26            | 26   | 26            | ampersand        | AMPERSAND              |

| 0027 | A9            |      |               | quotesingle      | APOSTROPHE-QUOTE       |

| 0028 | 28            | 28   | 28            | parenleft        | OPENING PARENTHESIS    |

| 0029 | 29            | 29   | 29            | parenright       | CLOSING PARENTHESIS    |

| 002A | 2A            | 2A   |               | asterisk         | ASTERISK               |

| 002B | 2B            | 2B   | 2B            | plus             | PLUS SIGN              |

| 002C | 2C            | 2C   | 2C            | comma            | COMMA                  |

| 002D | 2D            | AD   |               | hyphen           | HYPHEN-MINUS           |

| 002D |               | 2D   |               | minus            | HYPHEN-MINUS           |

| 002E | $2\mathrm{E}$ | 2E   | $2\mathrm{E}$ | period           | PERIOD                 |

| 002F | 2F            | 2F   | $2\mathrm{F}$ | slash            | SLASH                  |

| 0030 | 30            | 30   | 30            | zero             | DIGIT ZERO             |

| 0031 | 31            | 31   | 31            | one              | DIGIT ONE              |

| 0032 | 32            | 32   | 32            | two              | DIGIT TWO              |

| 0033 | 33            | 33   | 33            | three            | DIGIT THREE            |

| 0034 | 34            | 34   | 34            | four             | DIGIT FOUR             |

| 0035 | 35            | 35   | 35            | five             | DIGIT FIVE             |

| 0036 | 36            | 36   | 36            | six              | DIGIT SIX              |

| 0037 | 37            | 37   | 37            | seven            | DIGIT SEVEN            |

| 0038 | 38            | 38   | 38            | eight            | DIGIT EIGHT            |

| 0039 | 39            | 39   | 39            | nine             | DIGIT NINE             |

| 003A | 3A            | 3A   | 3A            | colon            | COLON                  |

| 003B | 3B            | 3B   | 3B            | semicolon        | SEMIKOLON              |

Tabelle 1.11: UNICODE to Adobe Standard Mappings

| UNIC | 6862.2 | SGML                | Unicode character name    |

|------|--------|---------------------|---------------------------|

| 0021 |        | excl                | EXCLAMATION MARK          |

| 0023 |        | num                 | NUMBER SIGN               |

| 0024 |        | dollar              | DOLLAR SIGN               |

| 0025 |        | percnt              | PERCENT SIGN              |

| 0026 |        | amp                 | AMPERSAND                 |

| 0027 |        | quot                | APOSTROPHE-QUOTE          |

| 0028 |        | lpar                | OPENING PARENTHESIS       |

| 0029 |        | rpar                | CLOSING PARENTHESIS       |

| 002A |        | ast                 | ASTERISK                  |

| 002B | 05.00  | plus                | PLUS SIGN                 |

| 002C |        | comma               | COMMA                     |

| 002D |        | hyphen              | HYPHEN-MINUS              |

| 002E |        | period              | PERIOD                    |

| 002F |        | sol                 | SLASH                     |

| 003A |        | colon               | COLON                     |

| 003B |        | semi                | SEMICOLON                 |

| 003C |        | lt                  | LESS-THAN SIGN            |

| 003D |        | equals              | EQUALS SIGN               |

| 003E |        | $\operatorname{gt}$ | GREATER-THAN SIGN         |

| 003F |        | quest               | QUESTION MARK             |

| 0040 |        | commat              | COMMERCIAL AT             |

| 005B |        | lsqb                | OPENING SQUARE BRACKET    |

| 005C |        | bsol                | BACKSLASH                 |

| 005D |        | rsqb                | CLOSING SQUARE BRACKET    |

| 005E |        | circ                | SPACING CIRCUMFLEX        |

| 005F |        | lowbar              | SPACING UNDERSCORE        |

| 0060 |        | grave               | SPACING GRAVE             |

| 007B |        | lcub                | OPENING CURLY BRACKET     |

| 007C |        | verbar              | VERTICAL BAR              |

| 007D |        | rcub                | CLOSING CURLY BAR         |

| 007E |        | tilde               | TILDE                     |

| 00A0 |        | nbsp                | NON-BREAKING SPACE        |

| 00A1 |        | iexcl               | INVERTED EXCLAMATION MARK |

| 00A2 |        | cent                | CENT SIGN                 |

| 00A3 |        | pound               | POUND SIGN                |

Tabelle 1.12: The UNICODE to SGML (ISO DIS  $6862.2)\ \mathrm{Mappings}$

| UNIC | ROM | SYM | GRK            | GK2 | HEB             | ARB             | NAME                   |

|------|-----|-----|----------------|-----|-----------------|-----------------|------------------------|

| 0020 | 20  | 20  | 20             | 20  | 20/A0           | 21/A1           | SPACE                  |

| 0021 | 21  | 21  | $\frac{1}{21}$ | 21  | 21/A1           | 21/A1           | ECLAMATION MARK        |

| 0022 | 22  |     | 22             | 22  | 22/A2           | 22/A2           | QUOTATION MARK         |

| 0023 | 23  | 23  | 23             | 23  | $\frac{23}{A3}$ | $\frac{23}{A3}$ | NUMBERSIGN             |

| 0024 | 24  |     | 24             | 24  | 24/A4           | 24/A4           | DOLLAR SIGN            |

| 0025 | 25  | 25  | 25             | 25  | 25/A5           | $25^{'}$        | PERCENT SIGN           |

| 0026 | 26  | 26  | 26             | 26  | 26              | 26/A6           | AMPERSAND              |

| 0027 | 27  |     | 27             | 27  | 27/A7           | 27/A7           | APOSTROPHE-QUOTE       |

| 0028 | 28  | 28  | 28             | 28  | 28/A8           | 28/A8           | OPENING PARENTHESIS    |

| 0029 | 29  | 29  | 29             | 29  | 29/A9           | 29/A9           | CLOSING PARENTHESIS    |

| 002A | 2A  |     | 2A             | 2A  | 2A/AA           | ,               |                        |

| 002B | 2B  | 2B  | 2B             | 2B  | 2B/AB           | 2B/AB           | PLUS SIGN              |

| 002C | 2C  | 2C  | 2C             | 2C  | 2C/AC           | 2C              | COMMA                  |

| 002D | 2D  |     | 2D             | 2D  | 2D/AD           | 2D/AD           | HYPHEN-MINUS           |

| 002E | 2E  | 2E  | 2E             | 2E  | 2E/AE           | 2E/AE           | PERIOD                 |

| 002F | 2F  | 2F  | 2F             | 2F  | 2F/AF           | 2F/AF           | SLASH                  |

| 0030 | 30  | 30  | 30             | 30  | 30/B0           | 30              | DIGIT ZERO             |

| 0031 | 31  | 31  | 31             | 31  | 31/B1           | 31              | DIGIT ONE              |

| 0032 | 32  | 32  | 32             | 32  | 32/B2           | 32              | DIGIT TWO              |

| 0033 | 33  | 33  | 33             | 33  | 33/B3           | 33              | DIGIT THREE            |

| 0034 | 34  | 34  | 34             | 34  | 34/B4           | 34              | DIGIT FOUR             |

| 0035 | 35  | 35  | 35             | 35  | 35/B5           | 35              | DIGIT FIVE             |

| 0036 | 36  | 36  | 36             | 36  | 36/B6           | 36              | DIGIT SIX              |

| 0037 | 37  | 37  | 37             | 37  | 37/B7           | 37              | DIGIT SEVEN            |

| 0038 | 38  | 38  | 38             | 38  | 38/B8           | 38              | DIGIT EIGHT            |

| 0039 | 39  | 39  | 39             | 39  | 39/B9           | 39              | DIGIT NINE             |

| 003A | 3A  | 3A  | 3A             | 3A  | 3A/BA           | 3A/BA           | COLON                  |

| 003B | 3B  | 3B  | 3B             | 3B  | 3B/BB           | 3B              | SEMICOLON              |

| 003C | 3C  | 3C  | 3C             | 3C  | 3C/BC           | 3C/BC           | LESS-THAN SIGN         |

| 003D | 3D  | 3D  | 3D             | 3D  | 3D/BD           | 3D/BD           |                        |

| 003E | 3E  | 3E  | 3E             | 3E  | 3E/BE           | 3E/BE           | GREATER-THAN SIGN      |

| 003F | 3F  | 3F  | 3F             | 3F  | 3F/BF           | 3F              | QUESTION MARK          |

| 0040 | 40  |     | 40             | 40  | 40              | 40              | COMMERCIAL AT          |

| 0041 | 41  |     | 41             | 41  | 41              | 41              | LATIN CAPITAL LETTER A |

| 0042 | 42  |     | 42             | 42  | 42              | 42              | LATIN CAPITAL LETTER B |

| 0043 | 43  |     | 43             | 43  | 43              | 43              | LATIN CAPITAL LETTER C |

| 0044 | 44  |     | 44             | 44  | 44              | 44              | LATIN CAPITAL LETTER D |

| 0045 | 45  |     | 45             | 45  | 45              | 45              | LATIN CAPITAL LETTER E |

| 0046 | 46  |     | 46             | 46  | 46              | 46              | LATIN CAPITAL LETTER F |

| 0047 | 47  |     | 47             | 47  | 47              | 47              | LATIN CAPITAL LETTER G |

| :    |     |     |                |     |                 |                 |                        |

Tabelle 1.13: UNICODE to Macintosh Mappings  $^{33}$

# Unicode 4.0.0 kommt mit 1226 neuen Zeichen

Minderheitensprachen wie Limbu, Tai Le oder Osmanya aufgestockt. Auch die sonst oft vernachlässigten historischen Schriften bekamen eine den Schriftzeichen für Sprachen wie Indisch, Khmer oder Arabisch hinzugefügt. Außerdem wurde das neue Release um die Zeichensätze von Erweiterung. Damit reagierte das Consortium auf Probleme bei vorherigen Unicode-Versionen[3]. Diese waren nicht zur Formulierung von XML-Tags für einige historische Zeichensätze wie Alt-Mongolisch, Burmesisch oder einige kanadische Indianerschriften fähig Wesentliche Bestandteile von Unicode 4.0 sind neue Symbole für den mathematisch und technischen Bereich, viele individuelle Zeichen wurden zu Das Unicode Konsortium[1] hat die Major-Version Unicode 4.0.0[2] vorgestellt. In der neuen Version wurden 1226 neue Zeichen integriert.

Industriegrößen wie Apple, Hewlett-Packard, IBM, Microsoft, Oracle, SAP oder Sun eingesetzt. Genauere Informationen über die neue Version natürlich, dass der Computer beziehungsweise das ausgeführte Programm das Unicode-System unterstützt. Der Unicode-Standard wird von Durch dieses System wird es möglich, einem Computer "weltweit" zu sagen, welches Zeichen man dargestellt bekommen will. Voraussetzung ist Unicode ist ein System, in dem die Zeichen oder Elemente aller bekannten Schriftkulturen und Zeichensysteme computertauglich festgehalten werden finden sich in der Dokumentation zu Unicode 4.0.0[4] und in der Unicode Character Database[5]. (see[6]/c't)

# URL dieses Artikels:

http://www.heise.de/newsticker/data/see-28.04.03-002/

# Links in diesem Artikel:

- [1] http://www.unicode.org/

- [2] http://www.unicode.org/versions/Unicode4.0.0/

- [3] http://www.heise.de/newsticker/data/hps-18.10.02-000/

- [4] http://www.unicode.org/versions/Unicode4.0.0/

- [5] http://www.unicode.org/ucd/

- [6] mailto:see@et.heise.de

# Bemerkung: Byteadressierte Computersysteme

# Memory Contents for Little and Big Endian Example

| ADDRESS | DATA |

|---------|------|

| 1000H   | 12H  |

| 1001H   | 34H  |

| 1002H   | 56H  |

| 1003H   | 78H  |

| 1004H   | 9AH  |

| 1005H   | ВСН  |

| 1006H   | DEH  |

| 1007H   | F0H  |

Abbildung 1.9: Die Bytes im Speicher ...

| Access             | Example         | Register Contents<br>(Little Endian) | Register Contents<br>(Big Endian) |

|--------------------|-----------------|--------------------------------------|-----------------------------------|

| Byte at 1000H      | ldob 0x1000, r3 | 12H                                  | 12H                               |

| Short at 1002H     | ldos 0x1002, r3 | 7856H                                | 5678H                             |

| Word at 1000H      | ld 0x1000, r3   | 78563412H                            | 12345678H                         |

| Long-Word at 1000H | ldl 0x1000, r4  | 78563412H (r4)<br>F0DEBC9AH (r5)     | 12345678H (r4)<br>9ABCDEF0H (r5)  |

Abbildung 1.10: ... und ihre Reihenfolge im Computerwort

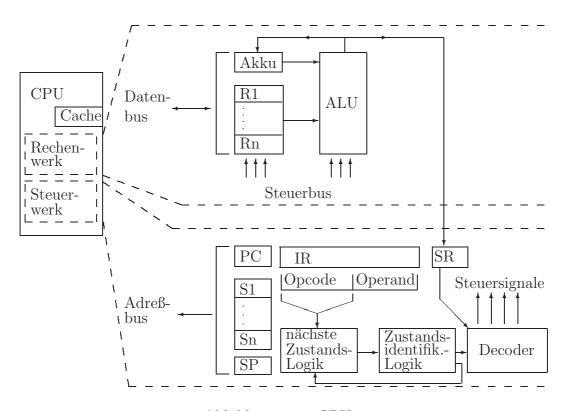

# Im Inneren der CPU

In einer CPU wurden zunächst

Abbildung 1.11: CPU

die einzelnen Aktionen hardwaremäßig (1 aus N Auswahl der gewünschten Aktion der ALU über CPU-interne Steuerleitungen) realisiert.

Die Maschinenbefehle einer typischen Intel-CPU sind unter http://taurus.ubishops.ca/ljensen/asm/intelasm.htm inspizierbar.

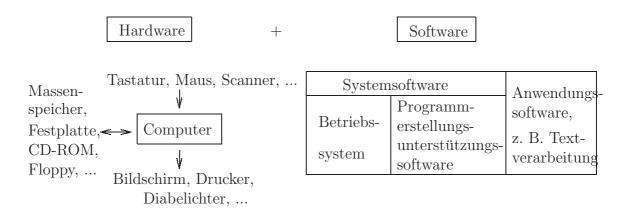

# 1.2 Modularer Aufbau von Betriebssystemen

Betriebssysteme haben die folgenden Aufgaben:

- Auftragsverwaltung (Jobs)

- Betriebsmittelverwaltung:

- Hauptspeicherverwaltung

- Dateiverwaltung

- E/A-Steuerung / Gerätetreiber

- Ablaufsteuerung / Prozess-/Taskverwaltung

- Zugriffskontrolle

- Ausnahmebehandlung

- ...

- Dienste / Services

Sie setzen sich dabei modular aus Subsystemen zusammen:

Abbildung 1.12: Windows 95/98

Abbildung 1.13: Windows NT

Abbildung 1.14: Solaris/Linux

# In der folgenden Skizze

Abbildung 1.15: Microcode und Betriebssystem

wird auf Microprogramming (Microcode) hingewiesen. Was ist darunter zu verstehen?

# 1.3 CISC/RISC

### 1.3.1 CISC

Traditionelle CISC's (= complex instruction set computers) sind:

- IBM360

- DEC VAX

- Intel 80386 (80x86)

- Motorola 68030 (680x0)

- ...

Akku CPU R1Daten-ALU Cache bus Rn Rechen-werk 111 Steuer-Steuerbus werk PCSRIR Opcode Operand Steuersignale S1۱ Adreßt bus nächste Zustands-identifik.-Sn Zustands-Decoder SP logik logik

Abbildung 1.16: CISC-CPU-Aufbau

In Zeiten, als der Zeitraum zur Übertragung eines Datenwortes vom Speicher in ein Register oder umgekehrt Größenordnungen länger dauerte als ein

einfacher logischer oder arithmetischer Primitiv-Befehl, mußte zunächst die Programmabarbeitung durch wait-states künstlich verlangsamt werden. Man versuchte dann aus Gründen der Ökonomie, eine CPU immer komplexere Primitiv-Befehle (deren Ausführungszeit lediglich anfangs immer noch höchstens eine "Datentransferzeit Register in Speicher" lang war) ausführen zu lassen. In der damaligen Zeit waren dafür jedoch nicht genügend Schaltoperationen auf einem Chip realisierbar, weshalb man das Rechenwerk der CPU wiederum als Computer aufbaute:

Computer im Computer: Steuerwerk PC IR Opcode [Operand]  $\mu$ Programm-Steuersignale Adreß-Logik für Microcodeoperationen(ALU)  $\mu$ P-Speicher  $\mu P-PC$  $\mu P-IR$ Decoder Ausführungseinheit Bedingungsgatter (Status)

Abbildung 1.17: Microprogrammierte CISC-CPU

Software ("SW") reduziert den Schaltungsaufwand (= Anzahl der Gatter, Anzahl der Leitungen, . . . ) und "interpretiert" den Maschinencode der CPU (Computer im Computer).

Eventuell werden sogar "noch" Nanoprogramme benutzt (68000er, ...):

Abbildung 1.18: Nanoprogrammierte CISC-CPU

### Das CISC-Designprinzip:

Reduziere die "semantic gap" zwischen Maschinensprache und Hochsprache durch

- viele komplexe Maschinenbefehle ( $\gtrsim 200$ ), etwa "case", "while", . . .

- viele Adressierungsmodi, etwa für "Felder", "Verbunde", . . .

- Unterprogramm-Management im Maschinencode

unter besonderer Beachtung der mindestens um den Faktor 10 langsameren Transferbefehle zum/vom Speicher.

# 1.3.2 "Überalterung" von CISC

Ungefähr 1970 wird

- die Komplexität des Microprogramms immer schlechter zu managen

- der Speicherzugriff schneller

- lohnt sich ein Redesign aufgrund von Messungen "typischer" Anwendungen:

Tabelle 1.14: Analyse typischer Computeranwendungen auf ihre Instruktionstypen hin

|            | SAL              | XPL            | FORTRAN      | С                | Pascal           |

|------------|------------------|----------------|--------------|------------------|------------------|

| %-         | Operating System | Systempgm.     | num. Pgm.    | Systempgm.       | Systempgm.       |

| Verteilung | Tanenbaum (1978) | Wortman (1972) | Knuth (1971) | Patterson (1982) | Patterson (1982) |

| :=         | $47^{1)}$        | 55             | 51           | 38               | 45               |

| if         | 17               | 17             | 10           | 43               | 29               |

| call       | 25               | 17             | 5            | 12               | 15               |

| loop       | 6                | 5              | 9            | 3                | 5                |

| goto       | 0                | 1              | 9            | 3                | 0                |

| sonstiges  | 5                | 5              | 16           | 1                | 6                |

Dabei sind in  $\,^{1)}$ 80% der Wertzuweisungen von dem einfachen Typ "Variable := Wert".

Konsequenz: Der Overhead durch das komplexe Microprogramm und die vielen Adressierungsmodi wird nur sehr selten auch ausgenutzt.

# MOV (80286/80386)

Move

**Instruction:** Move

Typical clocks: (80286) 2-19, (80386) 2-22

Description: Copies the source to the destination

**Operation:** There are several MOV instructions, all of which have the same function. They all copy the source operand's contents into the destination

operand without destroying the source.

Syntax: MOV destination, source

Flags affected: None Flags undefined: None

**Protected mode exceptions:** A general protection exception, stack fault exception, or descriptor not present exception may be generated if a segment register is being loaded. A general protection exception also may be generated if the destination is in a nonwritable segment. If the CS, DS, or ES segment contains an illegal memory operand effective address, a general protection exception is generated. If the SS segment contains an illegal address, a stack fault exception is generated.

**Real address mode exceptions:** When a word operand is at offset 0FFFFH, INT 13 is generated.

**80386 note:** Word size is 32 bits. Memory addresses are formed using 32-bit effective addresses or 32-bit displacement.

Abbildung 1.19: Der x86 MOV-Befehl

### MUL (80286/80386)

Multiply, unsigned

Instruction: MUL

Typical clocks: (80286) 13-21, (80386) 9-41

**Description:** Performs unsigned multiply  $(AX = AL \times specified byte)$

Performs unsigned multiply (DX:AX =  $AX \times$  specified word)

**Operation:** A byte operand of the MUL instruction causes the byte to be multiplied by the AL register and the result left in the AX register. CF and OF are reset to 0 if AH is 0; otherwise, they are set to 1.

A word operand of the MUL instruction causes the word to be multiplied by the AX register and the result left in DX:AX. DX contains the high-order 16 bits of the result. CF and OF are reset to 0 if DX is 0; otherwise, they are set to 1. See the 80386 note.

Syntax: MUL source

Flags affected: OF, CF

Flags undefined: SF, ZF, AF, PF

**Protected mode exceptions:** If the CS, DS, or ES segment contains an illegal memory operand effective address, a general protection exception is generated. If the SS segment contains an illegal address, a stack fault exception is generated.

**Real address mode exceptions:** When a word operand is at offset 0FFFFH, INT 13 is generated.

Abbildung 1.20: Der x86 MUL-Befehl

# 1.3.3 RISC (= reduced instruction set computer)-Designprinzip

- Analysiere Anwendungen, um die Schlüsseloperationen zu finden.

- Reduziere unter allen Umständen die "Datenpfadzykluszeit" (Register  $\rightarrow$  ALU  $\rightarrow$  Register) für diese Operationen, also: keine Microcode Interpretation (Maschinencode = Microcode)

- Jedes "neue" Feature ist nur zuzulassen, wenn es häufig benutzt wird und die Mehrzahl der existierenden nicht verlangsamt.

(Wiederhole diesen Design-Zyklus für die anderen CPU-Ressourcen: Cache, Speichermanagement, Gleitkomma-Koprozessoren, . . . )

Tabelle 1.15: Von CISC zu RISC

|                        |         | CISC          |        | RISC    |          |          |  |

|------------------------|---------|---------------|--------|---------|----------|----------|--|

|                        | IBM     | IBM VAX Xerox |        |         | Berkeley | Stanford |  |

|                        | 370/168 | 11/780        | Dorado | 801     | RISC I   | MIPS     |  |

| Jahr                   | 1973    | 1978          | 1978   | 1980    | 1981     | 1983     |  |

| # Operationen          | 208     | 303           | 270    | 120     | 39       | 55       |  |

| Microcode-Größe [byte] | 54K     | 61K           | 17K    | _       | _        | _        |  |

| Befehlslänge [byte]    | 2-6     | 2–57          | 1–3    | 4       | 4        | 4        |  |

| Ausführungsmodell      | reg-reg | reg- reg      | stack  | reg-reg | reg-reg  | reg-reg  |  |

|                        | reg-men | reg-men       |        |         |          |          |  |

|                        | men-men | men-men       |        |         |          |          |  |

CISC- und RISC-Architekturen lassen sich durch einige charakteristische Merkmale voneinander unterscheiden:

Tabelle 1.16: Unterscheidungsmerkmale CISC/RISC

|    | Bei RISC üblich                          | Bei CISC üblich                              |

|----|------------------------------------------|----------------------------------------------|

| 1. | einfache Befehle, 1 Befehl/Zyklus        | komplexe Befehle, 1 Befehl/viele Zyklen      |

| 2. | LOAD/STORE-Architektur                   | mem-reg, mem-mem Befehle                     |

|    | (nur LOAD/STORE greift auf Speicher zu)  |                                              |

| 3. | pipelined                                | kaum pipelined                               |

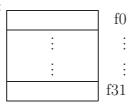

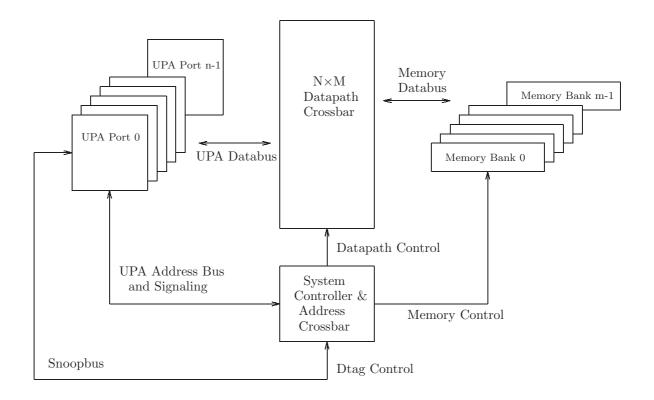

| 4. | Hardware, kein Microcode                 | Microcode                                    |